摘 要

本系统是以STM32F407为核心,主要采用FIFO来做高速缓存。高速信号先通过AD采样,然后先将采样后的数据给FIFO先缓存处理,然后再通过STM32F407进行加Blackman预处理,再做1024个点FFT进行频谱分析,最后将数据显示在LCD12864上,以便进行人机交互!该系统可实现任意波形信号的频谱显示,以及可以自动寻找各谐波分量的幅值,频率以及相位并进行8位有效数据显示。

系统设计任务

设计并制作一个高速频谱分析仪。

本系统由前置匹配放大电路,AD采样电路,高速FIFO缓存电路,以及液晶显示电路组成。其中高速数据缓存电路,以及高精度的显示数据是本次设计的难点!下面分别论证这几个模块的选择。

1.1.1 MCU处理器的比较与选择

做DSP处理主要是要考虑到运算速度。

在处理器的选择上通常可以采用8位,16位或者32位的MCU,但由于在处理信号的过程中,通常会遇到快速傅里叶FFT算法,所以会遇到大量的浮点运算,而且一个浮点数要占用四个字节,故在处理过程中要占用大量的内存,同时浮点运算速度比较慢,所以采用普通的MCU在一定时间内难以完成,所以综合考虑运算速度和内存大小等因素。

本系统采用32位的STM32F407做为核心DSP处理器件,该芯片具有1MB的Flash闪存空间,196KB的SRAM空间,并且时钟频率达到了168MHz。程序运行于168MHz主频时,通过Flash取指令(不是内部SRAM),通过Dhrysone测试得到210DMIPS,主要采用ART加速器,可以最大限度的消除Flash存储器较慢从而限制MCU性能的发挥,这可以使CPU可以在所有工作频率下近乎零等待的方式,从Flash中运行程序。还有就是STM32F407带有硬件FPU处理单元,这样可以不用软件算法实现浮点运算,而直接采用硬件来实现浮点运算,这样就减小了编译器生成的代码量,并且使用更方便,浮点数只占用四个字节就可以表示的数据范围很大,因此不用担心计算后的数据溢出问题!进一步提高运算速度。

1.1.2 采样方法比较与选择

方案一 通过DDS集成芯片产生一个频率稳定度和精度相当高的方波信号作为时钟信号。

可选用直接数字频率合成(DDS)芯片AD9851,AD9851为ADI公司生产的高性能器件,可与单片机通过简单的接口完成串行或者并行通信。可完成外部输入频率控制字与芯片内部频率相位控制字之间的转换,可以非常容易的通过频率控制字调整输出频率,以及精确的调整输出信号的相位,输出信号幅值稳定,但是由于DDS控制也需要占用一部分MCU的IO口资源,并且DDS在价格上成本有点高。

方案二 直接由MCU产生PWM波做为采样时钟信号。

可直接由STM32F407产生的PWM波,可实现频率,占空比可调的方波。最快IO口翻转速度可以达到84MHz,可以轻松实现想要的采样频率。由于输出的是3.3V的幅值的电压,与外围芯片相连,需要经过电平转换芯片转成5V,才能作为外围芯片的时钟信号。

方案三 采样时钟信号选用Linear公司生产的LTC1799提供。

LTC1799是一款精准型振荡器,使用方便。它采用2.7V到5.5V单电源工作,并提供了轨至轨、占空比为50%的方波输出。CMOS输出驱动器确保了快速上升/下降时间和轨至轨开关操作。频率设定通过电阻器调节,电阻阻值在 的范围内变化,以选择处于100KHz到33MHz之间的任何一个频率。三态DIV输入负责决定驱动输出之前对主时钟进行1、10或100分频。

综合上述方案,选择方案三,采用一片LTC1799来产生15MHz的采样时钟信号。

1.1.3 AD采样芯片的论证与选择

方案一 采用MCU内部ADC对采样信号进行采样。

STM32F407内部最大转换速率为7.2MSPS,而且被采样信号的幅值只能在0V到3.3V之间,能测得动态范围小,难以满足要求。

方案二 采用TI公司的8位TLC5510A作为AD采样芯片。

TLC5510A是采用高速CMOS技术,8位的,最大转换速率为20MSPS的AD转换芯片。支持+5V电源供电,内部包含采样保持电路,输出带有高阻态模式,以及带有内部参考电阻。输出数据在时钟的下降沿有效,数据流水线结构导致了2.5个时钟的延时。而且高速AD普遍价格比较昂贵,在满足输入信号在2V以上动态范围,TI公司可供申请的高速AD芯片只有TLC5510A这一种。

综合上述方案,选择方案二,在精度要求不高场合,采用TLC5510A作为高速采样芯片。

1.1.4 高速数据缓存芯片的论证与选择

由于15MHz的高速数据流,如果中断来标记数据流的地址,由于MCU的中断响应时间有限,有12个时钟周期的中断延时,因此就需要外部存储器做高速数据缓存。

方案一 采用SRAM芯片作为外部高速数据缓存芯片。

采用IDT71024来做高速缓存,由于SRAM提供了地址线端口和数据输入和输出端口,如果用MCU来控制的SRAM的地址线,中断响应不过来是反应不过来,如果用计数器作为地址计数器,原理是可以,但是实际操作效果不佳。

方案二 采用FIFO芯片作为外部高速数据缓存芯片。

IDT7205是单向异步FIFO的典型芯片,由IDT公司生产的,是一种高速、低功耗的先进先出双端口存储缓冲器。这种FIFO芯片内部的双端口RAM具有2套数据线,分别执行输入和输出功能,各自独立的写读指针分别在写、读时钟的控制下顺序地从RAM中写、读数据。

综合上述方案,选择方案二,它无地址线,布线简单,只能是顺序存取。

系统理论分析与计算

DFT(离散傅里叶变换)是数字信号分析与处理中的一种重要变换,它可以使数字信号处理可以在频域内采用数值运算的方法进行,大大增加了数字信号处理的灵活性,但直接计算DFT的计算量与变换区间长度N的平方成正比,当N较大时,计算量太大,所以在快速傅里叶变换(FFT)出现以前,直接用DFT算法进行谱分析和信号的实时处理是不切实际的。

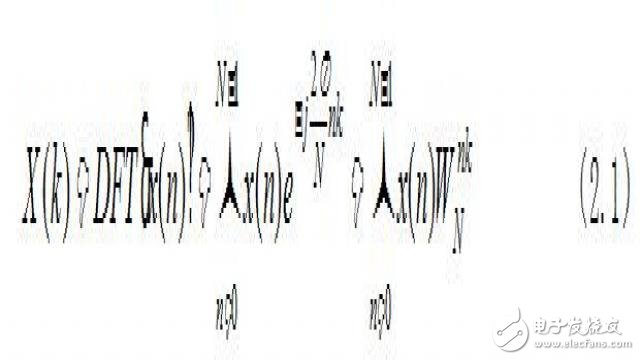

DFT的定义:设 是一个长度为N的有限长序列,定义 的N点离散傅里叶变换为

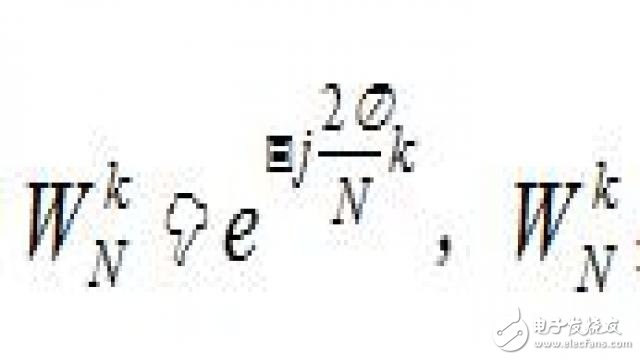

能提高DFT速度的唯一可利用的是因子 。 称为旋转因子

,

可表示为

具有以下两个重要性质。

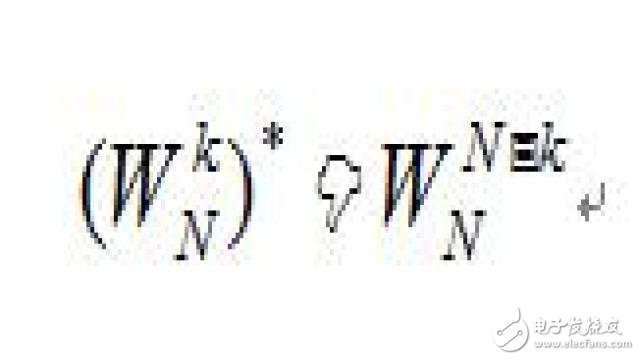

①对称性

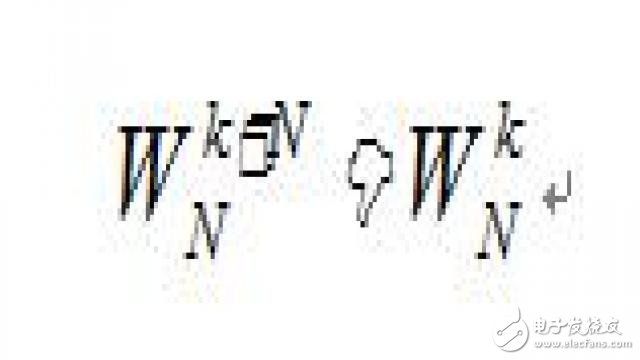

②周期性

利用 的周期性和对称性可把DFT的计算次数大大减小。

DFT分解法基本上分为两类:一类是将时间序列X(n) (n 为时间标号)进行逐次分解,由此得到的FFT算法称为按时间抽取算法,另一类是将傅里叶交换序列X(k) ( k为频率标号)进行分解,叫做按频率抽取算法。对每一算法,按基本的蝶形运算的构成又可分为基2、基4、基8以及任意因子等的FFT算法。不同基的FFT算法所需的计算量略有差异。之所以说略有差异是指并无数量级上的差异,甚至无成倍的差别。只是某种基的算法比另一种省几分之几而已。

而本方案采用的就是ST公司官方固件库里DSP库中已经写好的关于FFT的库函数,调用的是基4复数序列1024个点的FFT函数库。

假设FFT之后某点n用复数

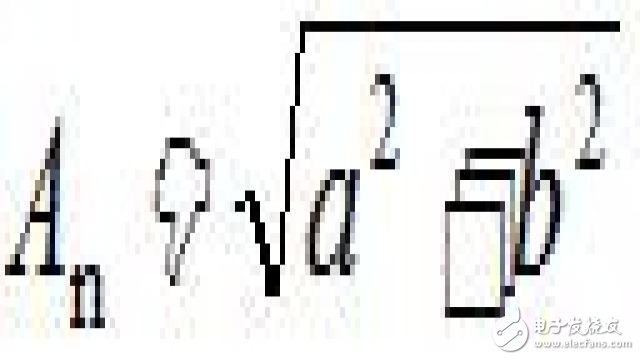

表示,那么这个复数的模就是

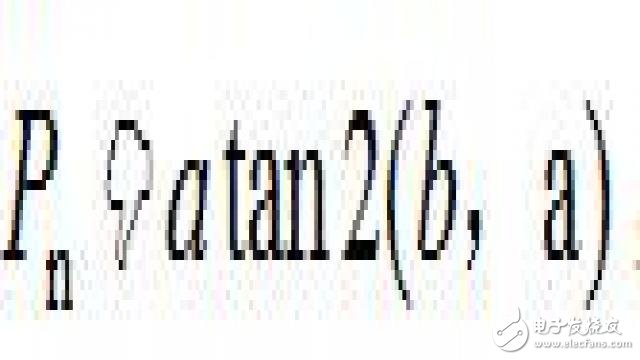

,相位就是

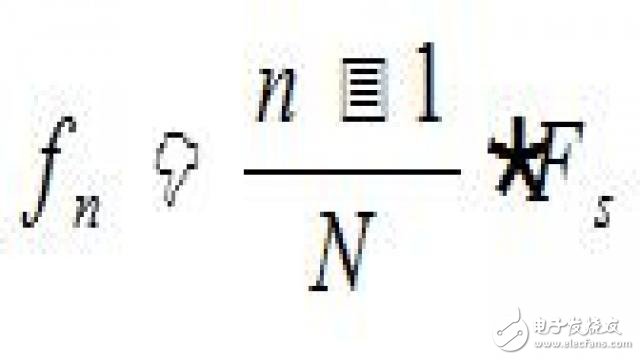

,频率就是

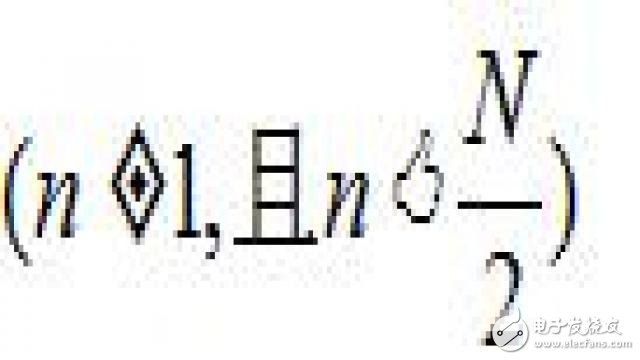

,(其中N表示FFT要做的点数,n表示排序的点,Fs为采样频率)。根据以上的结果,就可以计算出n点

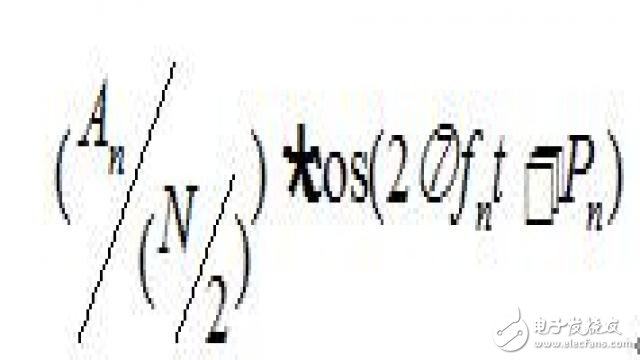

,

所对应信号的表达式为:

而对于n=1的点信号,是直流分量,幅度即为:

因此对于直流量要特殊考虑,一是幅值是其它频率点的2倍,二是直流量不含有相位信息。

但是由于所做的点数有限,其会造成频谱泄露是必然的。因此并非要计算所有点的幅值,相位以及频率信息,而只需要计算出各个峰值点的幅值,相位以及频率即可表示采样信号各谐波分量的全部信息。

因此算法模块要实现的功能:保存FFT之后峰值点的实部和虚部,以及峰值点所处的位置这几组点即可。

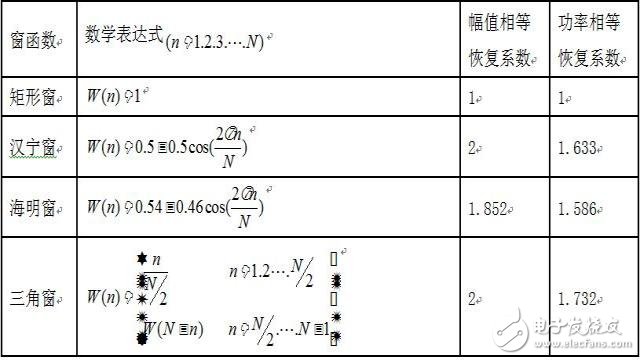

在频谱分析过程中,加窗是提高信号分析精度的一个重要措施,对加窗函数的基本要求:时域为改善截断处的不连续状态(由于吉布斯现象造成的振荡);频域为窗谱的主瓣窄而高,以提高分辨率,旁瓣幅值应小,正负交替接近相等,以减小泄露和假频。因此在选择窗函数的时候,应考虑被分析信号的性质和处理要求,如果仅要求精确求出主瓣频率,而不考虑幅值精度,则可选择用主瓣宽度比较窄而便于分辨的矩形窗,例如测量物体的自振频率等;如果分析窄带信号,且有较强的干扰噪声,则应选用旁瓣幅度较小的窗函数,如汉宁窗(Hanning)等。

为了使加窗函数后的功率谱和幅值谱不受窗函数的影响,必须根据一定的原则推导出恢复系数。加窗后的恢复系数一般遵守两个原则之一:幅值相等或能量相等的原则。

因此加窗模块要实现的功能:提高采样信号分析的幅值精度。

频谱分析中恢复系数的使用原则

在频谱分析中,根据不同用途采用不同恢复系数,在进行倍频程和三分之一倍频程分析时,为了使频带内总能量不变,一定要采用能量相等的恢复系数;而进行谱分析时,更关心的是各峰值频率对应的幅值,此时只能采用幅值相等的恢复系数。

常用的各种窗函数的恢复系数

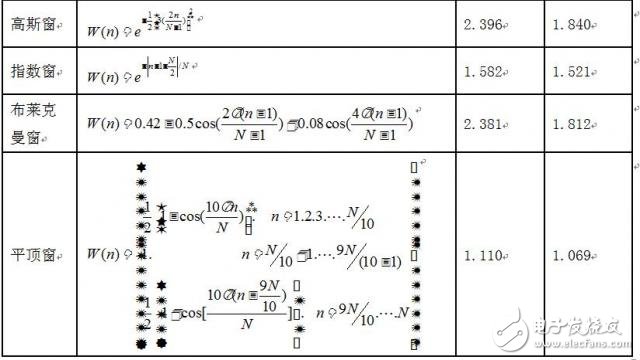

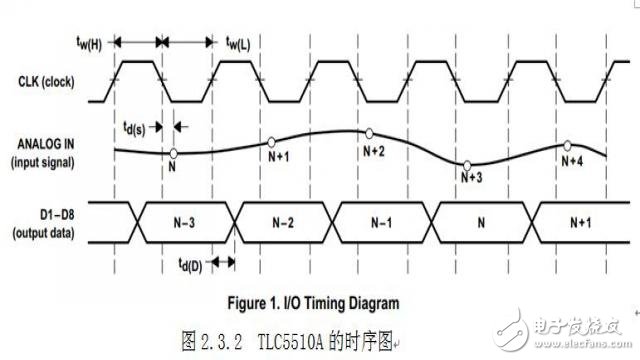

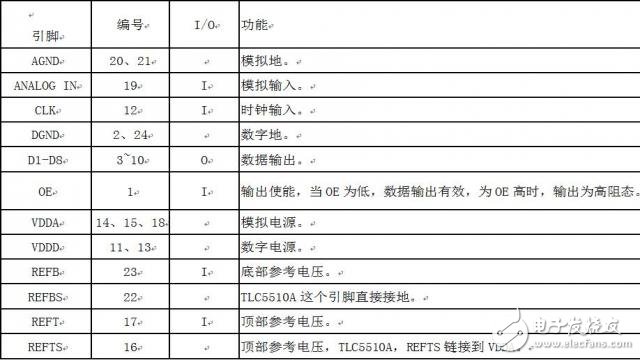

本系统采用的AD转换芯片为TLC5510A,TLC5510A是采用高速CMOS技术,8位的,最大转换速率为20MSPS的AD转换芯片。支持+5V电源供电,内部包含采样保持电路,输出带有高阻态模式,以及带有内部参考电阻。输出数据在时钟的下降沿有效,数据流水线结构导致了2.5个时钟的延时。虽然AD转换数据输出有2.5个时钟延时,但是只要量化的结果是正确的和数据是顺序输出,这个数据输出延时我们可以不用关心。外部还需要接一个4V的参考电压,这样才能量化到0V~4V的输入信号。TLC5510A引脚图和时序图如下:

图2.3.1 TLC5510A的引脚图

引脚功能描述:

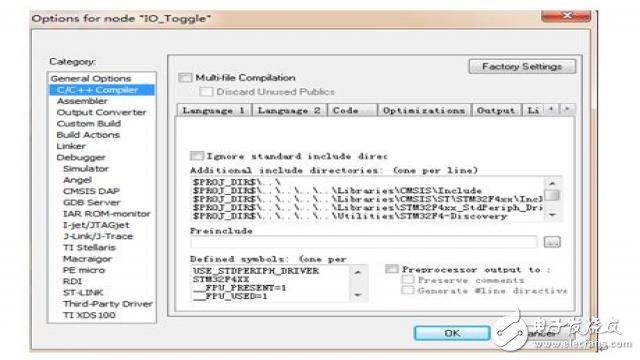

由于TLC4F的浮点功能,就需要使用固件库自带的arm_math.h,这个文件根据编译控制项(__FPU_USED == 1)来决定是使用那一种函数方法:如果没有使用FPU,那就调用keil的标准math.h头文件中定义的函数;如果使用了FPU,那就是用固件库自带的优化函数来解决问题。

在arm_math的开头部分是有这些编译控制信息:

#ifndef _ARM_MATH_H

#define _ARM_MATH_H

#define __CMSIS_GENERIC /* disable NVIC and SysTIck funcTIons */

#if defined (ARM_MATH_CM4)

#include "core_cm4.h"

#elif defined (ARM_MATH_CM3)

#include "core_cm3.h"

#elif defined (ARM_MATH_CM0)

#include "core_cm0.h"

#else

#include "ARMCM4.h"

#warning "Define either ARM_MATH_CM4 OR ARM_MATH_CM3...By Default building on ARM_MATH_CM4....."

#endif

#undef __CMSIS_GENERIC /* enable NVIC and Systick functions */

#include "string.h"

#include "math.h"

就是说如果不使用CMSIS的,就会调用keil自带的标准库函数。否则就用CMSIS的定义。这里因为是用的STM32F4固件库还提供了其他很有用的数学函数,都位于DSP_Lib文件夹。

3.有时候常会出现编译错误,会出现硬件错误,导致MCU锁住了,下不了程序。

解决方法就是硬件引导程序恢复

STM32F407虽然芯片资料说明端口可以忍受+5V的电压,但这不代表其可以识别+5的高电平,因此在读+5V的输入端口电平,需要用电平转换芯片将+5V转换成+3.3V的,否则读出的数据时一个错的。但是3.3V属于高电平,因此其可以驱动+5V工作的芯片。