经过几十年的发展,无线通信取得了巨大的进步,但通信设备的互通性差,一直制约着通信的进一步发展。有鉴于此,自1992年Jeo Mitola首次明确提出软件无线电(soft radio)的概念以来,软件无线电作为未来通信发展的方向,引起全世界人们的极大关注,并取得了迅猛的发展。软件无线电的中心思想是:构造一个开放的标准化、模块化的通用硬件平台,将各种功能由软件来完成。这样势必要把数字化处理(A/D和D/A变换)尽量靠近天线,那么A/D转换器就必须有足够的工作带宽、较高的采样速率,但这将导致成本成倍增加,因此,研发中常常只对中频进行数字化。本设计所用的核心芯片TMS320VC5509以及HSP50415成本低廉,应用广泛,可实现各种正交AM、PM调制,且功耗低,是实现中频发射机商业化的一个很好的途径。

1 主要芯片介绍

1.1 TMS320VC5509

本设计中的主要芯片为数字信号处理器DsP和数字上变频器HSP50415。DSP采用的是TMS320VC5509(简称:VC5509),它是TI公司最新推出的高性能、低功耗定点数字信号处理器,是目前功耗最低的新产品。在144MHz的时钟速率下,VC5509处理能力可达到400~800MIPS,指令周期可达6.94 ns,其中双乘累加器可以在l s内做400百万次相乘累加运算。

VC5509芯片具有丰富的CPU内部总线资源,有1条32位的程序数据总线(PB),5条16位的数据总线(BB、CB、DB、EB和FB)和6条24位的程序及地址总线,分别与CPU相连。这种并行的多总线结构,使其能在1个CPU周期内完成1个32位程序代码的读、3个16位数据的读和2个16位的写,这就使得其处理能力大大增强。

芯片中的核心单元由40位的移位器、40位的算术逻辑单元(ALU)、2个乘累加器(MAC)和若干寄存器构成,支持32位或双16位的并行计算。算术逻辑单元完成加、减、布尔逻辑操作等运算,能对本单元寄存器的内容进行测试、修改和移动,能在执行双16位时同时完成两个算术操作。

VC5509的地址总线是24位的,所以其寻址空问为16 MB。其片内存储器包括64 KB的ROM、192 KB的单存储RAM(SRAM)和64 KB的双存取RAM(DRAM),使得程序和数据能在片内高速传递,适时完成各种任务。DsP的存储空间分为两个独立的部分:统一的数据、程序空间(即在物理上相同)和I/O空间。只有在CPU读取指令时,程序空间才被访问,VC5509采用字节寻址来读取程序代码,即地址是按字节进行分配的,并且指令长度是可变的。在数据空间中,vc5509使用字寻址方式来读写8、16和32位数据,即地址按字进行分配。VC5509的I/O存储空间与数据/程序空间是分开的,它只用于对DSP片内的外设寄存器进行存取,采用的是16位寻址方式,其寻址范围是64位,当存取I/O空间时,要在16位地址前添加0以构成24位地址。

片内集成了丰富的外设资源,包括1个时钟发生器,2个可独立编程的定时器,1个通用输入输出口(GPIO),3个高速全双工的多通道缓冲串口(McBSP),1个增强型主机接口和DMA控制器,以及1个外部存储器接口。VC5509的CPU除了有限的片内存储器外,其余存储空间都需要通过外部存储器接口(EMIF)进行访问。VC5509将它的外部存储空间分为4个较小空间,每个空间用1个.选信号来指定(称为片选空间)。

为了实现低功耗,该芯片采用了两种省电方法:一种是关闭时钟方式;另一种是关闭电源方式。为了便于管理,VC5509还设有专门的省电寄存器。

上述特性使VC5509非常适合在数据传输率高、运算量大、又要求功耗低的应用场合,如在第2.5代和第3代移动通信中的应用。

1.2 HSP50415

HSFP50415是美国Intersil公司2000年推出的新一代数字上变频器(DUC),其功能是将数字基带信号进行调制变换成频带信号,同时完成上变频。通过对HSP50415不同的初始化,可以实现各种正交AM或PM调制,并可得到14位数字信号及12位的模拟信号。

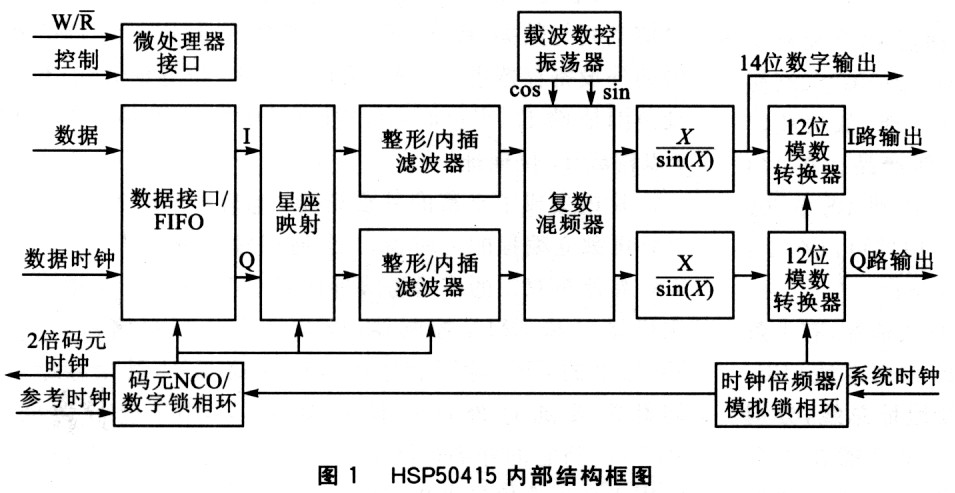

图1是HSP50415芯片的内部结构框图。由图1可知,HSP50415芯片是由微处理器接口、256深度的先进先出数据存储器(FIFO)、整形滤波器、内插滤波器、乘法器(矢量调制器)、载波数控振荡器、12位DAC等部分组成。

HSP50415对输入的数字信号进行采样和内插,降低了DSP的处理负担,优化了系统的性能。HSP50415的工作特点如下:

①最高输出采样率达100 MSPS,每路输入数据速率可达25 MSPS,而此时HSP50415的无寄生动态范围(SFDR)>70 dB.

②支持矢量调制模式.

③32位的码元速率和载波频率控制字可以十分精确地设定码元速率和载波频率。当} SP50415的主频输入为100 MHz时,载波设定可精确到O.050 3 Hz。

④片内提供有码元速率同步和数据猝发两种数据传输模式。

⑤HSP50415中有18个控制寄存器,可以灵活地配置载波频率、码元速率、FIFO的深度以及阈值、成形滤波器阶数及系数、增益控制、输出模式等参数,还可以灵活选择是否旁路某些模块(如整形滤波器或FIFO等),这就为硬件调试提供了方便。

⑥I、Q两路拥有高达256阶的FIR整形滤波器,可根据Intersil公司提供的软件自行设计滤波器。滤波器系数由微处理器接口写入芯片内部的4片64×72位RAM。

⑦内插滤波器可以实现输人到输出非整数倍的采样率转换。

⑧芯片中集成了2片12位DAC,可以方便地得到模拟输出。同时,HSP50415也提供了14位数字输出方式。

由此可见,HSP50415数字上变频器是一个功能强、应用方便的数字可编程器件。

2 系统设计方案

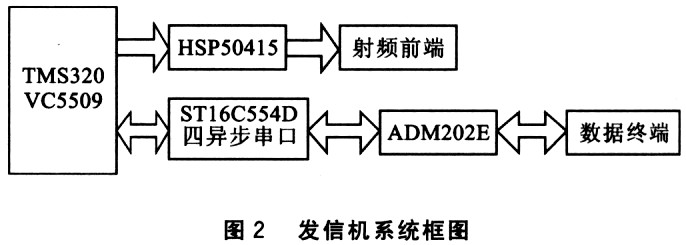

系统框图如图2所示。设计目标是将终端发送的数据由VC5509进行处理,加同步头,帧头等,而后送至HSP50415中,经过插值、混频至中频,输出12位模拟信号,最后由专门的发信机发出。图2中VC5509芯片用于完成数字信号处理以及控制功能,HSP50415芯片用于完成信号的插值、调制功能。

3 系统工作原理

本设计采用的是矢量调制方式(Vector Modulation)。数据由终端发出后,经串口发至DSP接收,。DSP读取后分I、Q两路交替送人14SP50415。HSP50415将接收数据串并变换后分成I、Q两路并行,其后经过星座映射,整形滤波和内插后,再将I、Q两路的数字基带信号搬移到中频上,其数学公式为:Outptlt=Ik cos(ω0t)±Qksin(ω0t)根据调制理论[1,-2]可知,当,k为基带输入信号,Ql为0时,即Output=S(t)cos(ω0t),Ik=S(t)这时,Output即为。DSP调制信号。当Qk是Ik的希尔伯特变换时,Output则得到SSB调制信号,“+”,“-”分别对应USB和LSB信号。之后,经X/sin(X)补偿滤波,12位的数模转换后,送入发信机,最终输出。

4 本设计方案的实现

4.1硬件电路图

上面已简述了发信机的设计方案及原理,下面重点说明本设计的硬件电路及其软件流程。

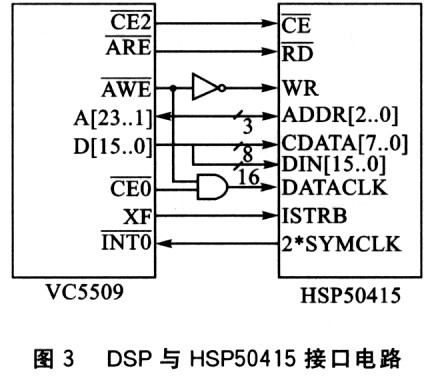

DSP与HSP50415的接口电路如图3所示,在此用了2个片选,分别用于对HSP50415初始化和向上变频芯片发送数据。在初始化开始时,选通CE2,通过微处理器接口对HSP50415进行初始化。初始化完成后,选通CE0,DSP每收到一个中断信号,就执行中断程序,CE0和AWE相“或”得出HSP50415的数据时钟,上变频芯片将在DATACLK的上升沿采样数据,再由程序对XF引脚拉高或拉低来控制采样的是I路还是Q路。中断信号由2*SYMCLK引脚产生。

4.2软件流程

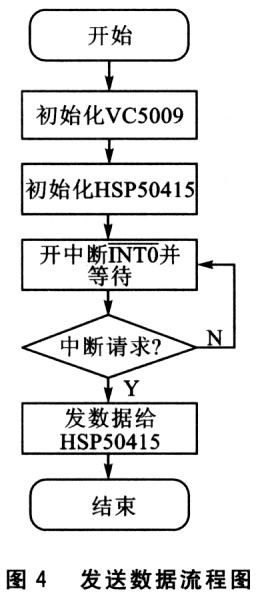

发送数据流程如图4所示。

在整个调试过程中,VC5509在软件控制和信号处理上起着重要的作用。对VC5509初始化主要包括设置时钟模式寄存器CLKMD,外部总线选择寄存器EBSEL,外部存储器接口EMIF等。中断向量表应建立一个子文件来存放。

对HSP50415的初始化即为对片内寄存器进行赋值,片内有18个控制寄存器可以根据需要写入。值得注意的是,整形滤波器的系数预先由sire415.exe产生,I、Q两路RAM为72位,而微处理器端口一次只接收8位数据,要根据资料要求进行9次写入。

5 结论

根据以上方案,笔者设计出调制方式为2FSK时,数据传输率为0.8 Mbps,调制方式为QPSK时,数据传输率为1.5 Mbps的无线电发信机。由于该系统采用软件化的设计方法,因此该软件无线电发信机可以根据用户的各种使用要求进行配置,而无需更改硬件,这就为用户降低了成本,并有利于对系统的升级换代。