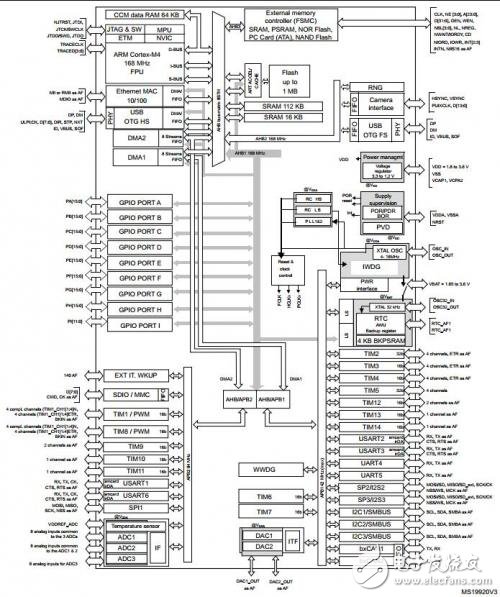

时钟系统是CPU的脉搏,就像人的心跳一样。STM32F4 的时钟系统比较复杂,不像简单的51 单片机一个系统时钟就可以解决一切。STM32F4 的框图如下(可以看到相应的时钟):

1. 连至 APB2 的定时器从 TIMxCLK 提供时钟 (最高 168 MHz) ,连至 APB1 的定时器从 TIMxCLK 提供时钟 (取决于RCC_DCKCFGR 寄存器中 TIMPRE 位的配置,最高 84 MHz 或 168 MHz)。

2. 摄像头接口和网络接口仅适用于 STM32F407xx 设备。

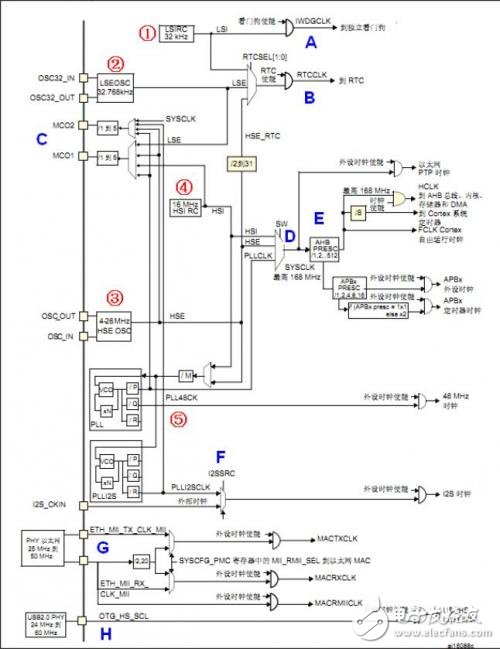

系统时钟图:

在STM32F4中,有5个重要的时钟源,为 HSI、 HSE、 LSI、 LSE、 PLL。 其中 PLL 实际是分为两个时钟源,分别为主 PLL 和专用 PLL。 从时钟频率来分可以分为高速时钟源和低速时钟源,在这 5 个中 HSI, HSE 以及 PLL 是高速时钟, LSI 和 LSE 是低速时钟。从来源可分为外部时钟源和内部时钟源,外部时钟源就是从外部通过接晶振的方式获取时钟源,其中 HSE 和LSE 是外部时钟源,其他的是内部时钟源。下面我们看看 STM32F4 的这 5 个时钟源,我们讲解顺序是按图中红圈标示的顺序:

①、 LSI 是低速内部时钟, RC 振荡器,频率为 32kHz 左右。供独立看门狗和自动唤醒单元使用。

②、 LSE 是低速外部时钟,接频率为 32.768kHz 的石英晶体。 这个主要是 RTC 的时钟源。

③、HSE 是高速外部时钟,可接石英/陶瓷谐振器,或者接外部时钟源,频率范围为 4MHz~26MHz。核心板接的是 8M 的晶振。 HSE 也可以直接做为系统时钟或者 PLL 输入。

④、 HSI 是高速内部时钟, RC 振荡器, 频率为 16MHz。 可以直接作为系统时钟或者用作 PLL输入。

⑤、 PLL 为锁相环倍频输出。 STM32F4 有两个 PLL:

1) 主 PLL(PLL)由 HSE 或者 HSI 提供时钟信号,并具有两个不同的输出时钟。

第一个输出 PLLP 用于生成高速的系统时钟(最高 168MHz)

第二个输出 PLLQ 用于生成 USB OTG FS 的时钟( 48MHz),随机数发生器的时钟和 SDIO时钟。

2) 专用 PLL(PLLI2S)用于生成精确时钟,从而在 I2S 接口实现高品质音频性能。

A. 这里是看门狗时钟输入。从图中可以看出,看门狗时钟源只能是低速的 LSI 时钟。

B. 这里是 RTC 时钟源,从图上可以看出, RTC 的时钟源可以选择 LSI, LSE,以及HSE 分频后的时钟, HSE 分频系数为 2~31。

C. 这里是 STM32F4 输出时钟 MCO1 和 MCO2。 MCO1 是向芯片的 PA8 引脚输出时钟。它有四个时钟来源分别为: HSI,LSE,HSE 和 PLL 时钟。 MCO2 是向芯片的PC9 输出时钟,它同样有四个时钟来源分别为: HSE,PLL, SYSCLK 以及 PLLI2S时钟。 MCO 输出时钟频率最大不超过 100MHz。

D. 这里是系统时钟。从图可以看出, SYSCLK 系统时钟来源有三个方面:HSI,HSE 和 PLL。在我们实际应用中,因为对时钟速度要求都比较高我们才会选用 STM32F4 这种级别的处理器,所以一般情况下,都是才用 PLL 作为 SYSCLK时钟源。根据前面的计算公式,大家就可以算出你的系统的 SYSCLK 是多少。

E. 这里我们指的是以太网 PTP 时钟, AHB 时钟, APB2 高速时钟, APB1 低速时钟。这些时钟都是来源于 SYSCLK 系统时钟。其中以太网 PTP 时钟是使用系统时钟。AHB,APB2 和 APB1 时钟是经过 SYSCLK 时钟分频得来。这里大家记住, AHB最大时钟为 168MHz, APB2高速时钟最大频率为 84MHz,而 APB1低速时钟最大频率为 42MHz。

F. 这里是指 I2S 时钟源。从图 可以看出, I2S 的时钟源来源于 PLLI2S 或者映射到 I2S_CKIN 引脚的外部时钟。 I2S 出于音质的考虑,对时钟精度要求很高。

G. 这是 STM32F4 内部以太网 MAC 时钟的来源。对于 MII 接口来说,必须向外部PHY 芯片提供 25Mhz 的时钟,这个时钟,可以由 PHY 芯片外接晶振,或者使用STM32F4 的 MCO 输 出 来 提 供 。 然 后 , PHY 芯 片 再 给 STM32F4 提 供ETH_MII_TX_CLK 和 ETH_MII_RX_CLK 时钟。对于 RMII 接口来说,外部必须提供 50Mhz 的时钟驱动 PHY 和 STM32F4 的 ETH_RMII_REF_CLK,这个 50Mhz时钟可以来自 PHY、有源晶振或者 STM32F4 的 MCO。

H. 这里是指外部 PHY 提供的 USB OTG HS( 60MHZ)时钟。