含有100M晶体管的逻辑处理器已经被成功地设计和生产。下一个主要目标是含有1G(10亿)晶体管的处理器。

历史上,提高处理器性能一直是半导体技术革新背后主要的驱动力-晶体管尺寸缩减30%可以使晶体管密度增长两倍,器件处理速度提高约50%(主要是因为载流子的迁移动距离更短了)。

最近,加拿大ATI公司将Radeon 9700投向市场,这是一种含有超过100M个晶体管的图形处理器。其竞争对手,美国Nvidia公司也将在今年早些时候将含100M个晶体管的处理器NV30推向市场。

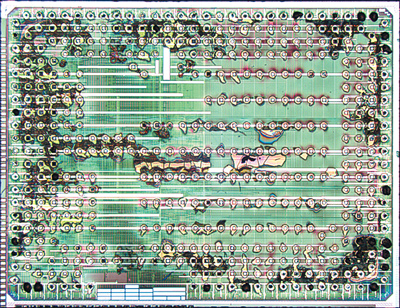

图1为Radeon 9700含两层金属布线,尺寸大小为14.8 x 14.8mm,不含大量缓存,因此逻辑晶体管数目真正达到了100M。现在的竞争目标是达到下一个重要的里程碑-1G晶体管处理器。

图1. ATI Radeon 处理器俯视图。

不管是高度的集成度,还是空前的功能和处理能力,1G处理器都将是一个重要的里程碑。本文将回顾目前的100 M晶体管技术,并简述制造1 G晶体管处理器所需要发展的半导体技术。当然,其他前沿领域的进展包括设计工具、测试方法和封装技术也是必不可少的。

历史的回顾

实现100M晶体管处理器的很多障碍都已攻克。它要求材料、设备、掩摸版制造和工艺技术等方面的一系列革新,以及世界各地的研发团队在设计和测试技术方面的研究进展。

要达到更高的集成度,不仅需要更先进的光刻和蚀刻工艺,还要求更小的P-N结和更合适的栅极介电质以优化晶体管性能,以及采用先进的内连线技术以减少RC延迟。

衍射引起的光刻限制不断地被波长更短的紫外(UV)光光刻技术所推动和克服。由此引起的景深问题(特别是在栅极)已经被浅沟隔离和化学机械抛光(CMP)技术解决。RC延迟问题也被波纹制铜工艺和金属间低k值介电材料(IMD)所解决。

在栅极和源漏极的pn结的扩散方面,采用多晶金属硅化物(Polycide)和金属硅化物(Silicide)来制备,以减小寄生电阻。金属硅化物一般使用硅化钨和硅化钛,但是现在已经被硅化钴所取代。通过增强栅极耦合,氮化硅侧墙隙壁(Spacer)可进一步减小LDD区域的阻值。

栅极长度的不断缩短会大大提高晶体管的处理速度,特别是高端处理器。2001年ITRS预言采用80nm水平的工艺,栅极的物理长度可以达到32nm。

栅氧化层的厚度也大大变薄了,并进行氮化以减小漏电和改善热载流子的可靠性。在衬底方面,平面离子注入技术取代了自对准双阱技术。Intel Northwood Pentium处理器的分析样品就很好地说明了这些技术的发展。

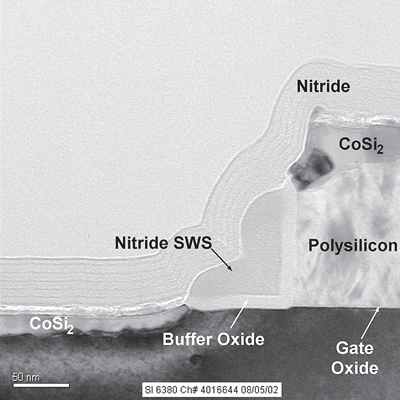

图2. NMOS晶体管高倍TEM截面图。

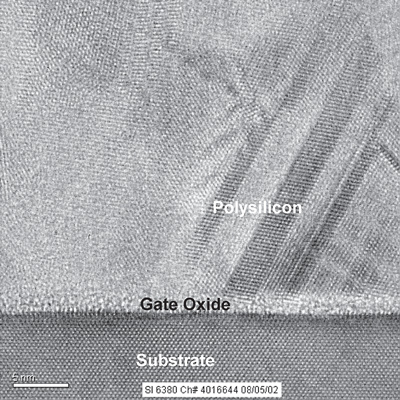

图2是该处理器中栅极长度最小的NMOS晶体管的TEM截面图。虽然该处理器名义上是用0.13um、6层金属布线工艺制备的,但栅极的物理长度仅为50nm。要注意的是栅极的侧墙是用氮化硅制备的。栅极和源/漏区域是用硅化钴制备的。器件阱区的扩展电阻分布图(图3)揭示了在3um厚、轻掺杂的外延单晶硅层上有一个深度分别为1.7um的N-阱和1.0um的P-阱区。图4 给出了其剖面图β。表明从IMD1层到IMD3层使用的都是低介电常数的氟氧化硅材料。图5给出了用制铜工艺制备出的6层金属连线结构。

图3. 栅极氧化层晶格边缘TEM图。

简而言之,通过使用更短波长的光刻技术、CMP技术、制铜技术和低k值介电质等技术,在MOS晶体管的基本结构没有改变的情况下,我们还是制备出了100M晶体管处理器,达到了一个新的里程碑。然而为了达到集成1G个晶体管的水平,目前所用的晶体管结构的重大改变将是不可避免的了。有两个关键的问题应该考虑解决,一个是通过栅介质层的沟道漏电流,一个是在关态下通过衬底的漏电流。这些漏电流将呈指数式增长。实际上,因为功耗太大,如果不能有效地减小这些漏电流,晶体管的进一步缩小将是不可能实现的。

图4. 金属互连介电层的SIMS剖面图。

向1G处理器进军

根据摩尔定律,1G处理器应该在2007年实现商业化生产。Intel院士John Crawford最近提出了1G处理器的概念,它包含4个 Intel Itanium2 核心处理器和一个共享缓存。该处理器采用65nm制造技术,栅极长度为30nm,等效氧化层厚度约为8nm。

现有的CMOS晶体管结构不可能被简单地缩减到这样的大小而不产生严重的问题。主要的问题存在于栅极介电质、栅电极、衬底和器件结构以及器件内连线等方面。下文将讨论这些因素在尺寸缩小时产生的主要问题和可能的解决方法。

栅极介电质

CMOS晶体管的电流驱动与栅极电容成正比,栅极电容又和栅极介电质的介电常数成正比。因此,使用具有更高介电常数的栅极介电质能解决栅极漏电流的两难问题。该方法可以在提高栅极介电质厚度以减小栅极漏电流的同时,保持晶体管驱动电流不变。

在许多高k介电质中,介电常数约为22的HfO2与多晶硅之间具有优越的热稳定性和很高的能隙,因此是最有希望在短期内应用的。好几个实验室的初步研究结果都已证明使用HfO2作为栅极介电质可以在保持驱动电流不变的情况下有效地阻止栅氧化层漏电。在相同的晶体管驱动电流下,HfO2的厚度可以比SiO2 (k=3.9)大5.6倍。以65nm技术为例,HfO2的厚度大约为4nm。HfO2的关键问题是可以接受的界面态函数、稳定性、缺陷密度和热载子效应可靠性。

还有一个办法是对栅氧化层进行深度氮化。NEC最近证明,厚度为1.5nm的栅氧化层深度氮化后栅极漏电流减小了100倍,可靠性提高了10倍。 2001 ITRS推测,至少到2007年,对于更注重处理速度而不是功耗的高端应用来说,这些技术已经绰绰有余。然而,对于1.0nm以下的薄膜来说,厚度和均匀性的控制将是一项新的挑战。

栅电极

目前,晶体管的栅电极主要是双重掺杂的多晶硅金属硅化物(Polycide)。然而,如果多晶硅掺杂过重,在偏压作用下,栅极和绝缘体的接触界面上会形成厚约0.5-1nm的耗尽区。耗尽区与栅氧化层串联在一起,使栅氧化层的有效厚度变大,从而导致电流驱动变小。

采用金属栅极可以消除该耗尽区。金属栅极同样有两个问题,一个是栅极电阻过大,第二个是PMOS工艺中的栅介质的硼穿透问题。

然而,必须注意使金属的功函数与NMOS和PMOS沟道相匹配。NMOS和PMOS可以采用中等能隙的单一金属或两种不同的、分别优化选择后的栅极金属。采用中等能隙的单一金属,工艺更简单,但是通常会有寄生效应,从而影响器件特性。为了保持很好的性能,反常规的超深度的(SSR)沟道掺杂是必须的。目前,正在开发一些难熔金属,包括钨和钼等作栅金属。可供选择的另一方法是通过完全的多晶硅硅化反应生成硅化钴来作栅电极。最近,还有报道说有人已经成功地制造了以HfO2为栅极介电质,TaSiN为NMOS栅电极,TiN为PMOS栅电极的晶体管。关键的工艺问题是如何使栅极和栅极介电质材料之间保持良好的相容性,以及如何将金属栅极整合到标准的CMOS工艺流程中。

硅衬底和器件结构

目前,高性能逻辑器主要的衬底是具有轻掺杂外延单晶层的重掺杂硅片。在未来几年中,为了不断提高速度和克服截止电流(Ioff)指数级增长的问题,这种结构也将产生变化。

饱和驱动电流很大程度上取决于VDD-Vt。但是为了保证电场值基本不变,VDD必须随着尺寸的减小而降低。因此,为了保持驱动电流不变,Vt必须随着VDD一起减小。然而,当Vt减小时,Ioff会呈指数级地增大。随之而来的问题是由于短沟道效应,栅极会逐渐失去控制,这是晶体管尺寸缩小时不可避免的结果。Sub-threshold Swing, DIBL和截止漏电流的增大都证明了这一现象。

根据Intel公布的数据,在0.13um技术中,栅极长度为0.07um时的Ioff (约10 nA/μm)比0.5um时的Ioff (<1 pA/μm)大104倍。当晶体管继续缩小时,预计工艺技术进步到65nm水平,栅极长度为30nm时,Ioff会继续提高一个数量级。当晶体管数目增长10倍达到1G时,功耗将比目前的含100M个晶体管的器件高两个数量级。

衬底漏电流必须减小。解决短沟道效应的方法是采用SOI衬底。SOI硅片在器件层底下埋有SiO2绝缘层, 该绝缘层能阻止漏电流和恢复长沟道的特性。该技术在IMB PowerPC产品上已应用多年。就象用铜工艺将铜用作内连线一样,它也将会成为主流技术。

器件内连线

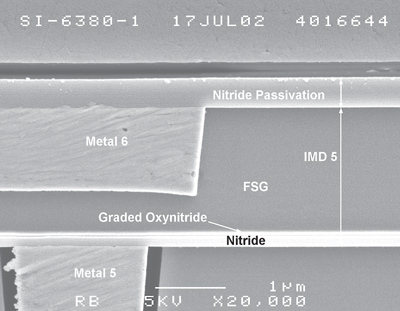

制铜工艺是0.13um工艺的主流内连线技术。Radeon 9700一共使用了8层金属布线。

1G处理器的内连线将会非常密集。ITRS预言65nm工艺将会用到10层金属内连线,导线宽度为150nm,每平方厘米上的内连线总长将达到11km。幸运的是,至少对于1G处理器,内连线的解决方案是相对没有问题的。制铜工艺将继续成为金属内连线的选择。然而,IMD将会很快地从目前的氟化硅玻璃(FSG)改为低介电常数的材料。最可能的替代材料是旋转涂布的聚合物如Dow Chemical公司的SiLK,或者是有机/无机混合物如Applied Material的黑金刚石和Novellus的CORAL。

最后,尽管对于1G晶体管处理器来说光学内连线并不是必不可少的,由于它没有RC延迟问题,因此人们对光学内连线在未来的器件中作为驱动时钟会很有兴趣。

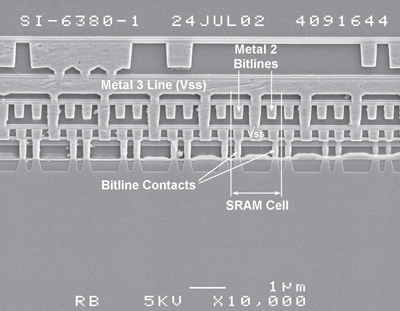

图5. SRAM区金属内连线SEM截面图。

结 论

当集成度超出1G的限制时,开发新的器件结构将是必不可少的。由于SOI 能截断衬底漏电的通道,从而消除衬底漏电流,因此科学家们基于SOI衬底提出了一些新的晶体管结构,包括单栅极DST晶体管、双栅极FinFET、平面双栅极晶体管和三栅极晶体管。

FinFET先是将SOI硅片表面的单晶硅层的厚度削减到几十个纳米,然后通过蚀刻形成一个粘附在硅片表面上、狭窄的、垂直方向上的鳍状物。沟道处于绝缘层的上面,鳍状物的里面。鳍状物的两端分别为源漏电极,而栅极则悬挂在两边。

平面双栅极晶体管则利用一种新颖的硅片粘接技术在很薄的单晶硅层两边形成栅电极。

三栅极晶体管的栅极长度与硅本体的宽度及高度相同。与单栅极结构不同,三栅极晶体管对硅厚度的要求要宽松得多。

硅基光电子学和MEMS的进展,很有希望在光学内连线方面取得突破。很难预测谁将首先达到1G逻辑处理器的水平。看起来不太可能是传统的微处理器制造商IBM或Intel,他们主要是为高容量、通用应用设计的。高性能计算(如图形处理器)或高度集成系统芯片的应用(如单片机电话)看起来是1G芯片研发的主要驱动力。无庸质疑的是,1G处理器的时代总会到来,因为芯片设计者总觉得晶体管不够用。