SoC设计人员现在可以通过使用可扩展的微处理器核来获得可与定制硬件相比的高效率,同时还可保持基于处理器设计的可编程性。通过允许SoC开发人员在处理器核中加入自定义的指令,具有可配置性和可扩展性的Xtensa处理器能够提供定制硬件设计和基于处理器设计两方面的优点。

本文通过使用TIE语言为Xtensa处理器添加除法指令来详细说明采用可扩展处理器的设计方法。Tensilica指令扩展语言TIE用于为处理器架构添加扩展指令和用户定义的寄存器。文中通过基于TIE的可扩展处理器实现了除法指令的添加,并将该方法与采用RTL Verilog实现的方法进行了比较。

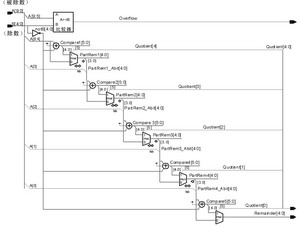

图1 10×5组合逻辑除法电路结构

图2 UDIV10x5指令编码

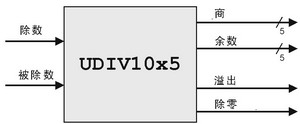

图3 UDIV10x5输入输出示意图

添加除法指令

尽管许多算法都需要除法和求模运算,但是大多数算法使用除法运算的频率要小于加法、减法或者乘法运算。而且,用于执行通用32位除法运算的硬件成本也很高。因此,绝大多数为DSP或嵌入式应用设计的商用微处理器都没有专门的除法指令,而是采用软件迭代算法来实现整数除法。

但是,如果在嵌入式处理器中缺少除法运算硬件,就可能会产生计算瓶颈。例如,在MPEG-1、MPEG-2、MPEG-4和H.263等视频编码标准中通常会进行量化操作,该操作将所有视频象素数据值与另一个数值相除,以减少存储每个象素时需要的数据位数。由于量化操作使用非常频繁,因此,采用专门的除法器将会大大提高视频编码的速度。然而,在采用了具有通用硬件除法指令的处理器架构后,SoC设计人员必须在性能提高和硅片面积增大之间做出权衡。这个问题对于专用领域就显得更加突出。例如,对于视频编码量化操作,象素值和用于量化的除数与处理器的数据宽度相比通常是很小的,因此,不需要通用的除法指令(该指令能够完成任何一个32位数的除法)来完成专门的量化操作。实际上,低精度的除法指令(该指令占用的硅片面积较小)也可以完成相同的量化操作。

同绝大多数处理器架构一样,考虑到硬件成本,基本的Xtensa处理器架构中并不包含通用的除法指令。然而,Xtensa处理器具有可配置和可扩展功能,因此,如果应用需要的话, SoC设计人员能够添加专门的除法指令和其它专用指令。具有添加正确指令的功能是可配置、可扩展处理器的重要特征,它使得设计人员可以构建出灵活、高效的高性能系统。

TIE语言令SoC设计人员能够通过添加专用指令和寄存器来方便、快速地扩展Xtensa处理器核。Xtensa处理器产生器采用TIE语言为定制的处理器产生RTL代码,并自动更新相关的软件工具,如C/C++编译器和指令集仿真器(ISS),使得软件工具可以更好地理解每条新指令的行为和时序特性。面向专用任务的可配置、可扩展处理器核可以实现高性能的SoC设计,它具有以下特点:能够有效地完成关键系统部件的硬件实现;由于采用了基于软件的算法实现,因此设计灵活性得到了提高;与纯硬件设计方法相比,自动化和集成化的设计和验证环境能够缩短产品的上市时间。

整数除法器的硬件设计

本文要设计一个硬件模块来完成一个10位的二进制被除数与一个5位的二进制除数的除法运算,产生一个5位的商和5位的余数。将此电路命名为10×5除法器,10和5分别表示被除数和除数的位数宽度。

设计除法器可以采用时序逻辑或组合逻辑两种方法,它们具有不同的优点。本文推荐采用组合逻辑的方法来实现除法器。与时序逻辑相比,该方法需要更多的逻辑门数,但是,在采用相同工艺技术的条件下,可以获得更快的运行速度。10×5除法器的组合逻辑电路如图1所示。

第一个比较器用于比较被除数A的高5位与除数B。如果A[9:5] >= B[4:0],那么除法操作将会产生一个大于5位输出精度的数,满足溢出条件。因此,硬件链路的第一级使用了一个比较器,而不是加法器。在第一个比较器之后,继续处理A[8:4],以及一系列加法、比较和移位操作。

带有扩展指令的除法

使用TIE处理器扩展指令来建立除法器硬件和用RTL代码实现非常相似。TIE语言是Verilog的子集,除法指令的TIE描述与等价的Verilog语句几乎相同。

通过使用TIE语言描述除法指令,可以使Xtensa处理器产生器知道如何产生适合Xtensa处理器流水线的除法器功能部件,如何为新指令增加软件工具的支持,以及如何更新指令集仿真器来对新指令建模。

选择一个命名和指令编码

设计一条新的处理器指令时,首先需要选择命名和指令编码。将本文中实现的10×5位的无符号除法指令命名为UDIV10x5,接着需要为该指令选择一个编码,这是在新指令中用于标识UDIV10x5的唯一编码子集。所有指令编码组都在Xtensa的24位指令空间中,设计人员可以在此空间中定义不与现有指令冲突的新指令编码。对于UDIV10x5指令,本文使用预先定义的CUST0指令代码空间(op0 或者 opcode field 0 = 0000b,及op1 或者 opcode field 1 = 0110b),并且进一步说明被op2指令标记的4位数在该指令中必须与0000b相等。命名和指令编码都通过TIE的“opcode”标志符来完成:

opcode UDIV10x5 op2=4'b0000 CUST0

新指令的指令编码如图2所示。

为处理器增加资源

接下来为Xtensa处理器核增加几个专用寄存器,用于保存除法运算的结果。首先,增加2个1位的寄存器用于保存溢出和除0结果。这些专用寄存器同基本Xtensa处理器架构中已提供给零开销循环(zero overhead loop)和桶形移位(barrier-shift)指令的专用寄存器相似。专用寄存器文件与通用寄存器文件是分离的。另外,还需增加第3个称为“udiv_remainder”的专用寄存器,用于存放UDIV10x5指令的5位余数结果。使用TIE的“state”标志符来增加这些专用寄存器。

state div_by_0 1

state overflow 1

state udiv_remainder 5

这些新增加的专用寄存器以后将会在TIE用于描述新指令功能的“reference”语句段中被访问,为了使程序员能够访问到这些专用寄存器,必须采用TIE的“user_register”标志符来说明每个寄存器的名称和编号。

user_register remainder 0 {udiv_remainder[4:0]}

user_register div_by_0 1 {div_by_0}

user_register overflow 2 {overflow}

通过上面3行TIE代码,就可以允许固件程序员通过C指令来对这些专用寄存器进行读写。

指令输入和输出描述

如果将除法指令看成一个黑盒子,那么它将如图3所示。

该信息通过TIE的“iclass”标志符传递给Xtensa处理器产生器。它描述指令使用的操作数,指令的C/C++和汇编语法,以及Xtensa处理器产生器产生的指令硬件模块的输入和输出。

对于UDIV10x5指令,假设10位的被除数和5位的除数均来自处理器的通用寄存器文件,而运算得到的5位商也存入该寄存器文件中。这些操作数由预先定义的指令编码中的源操作数和目的操作数域来说明,如图2所示。余数、溢出和除零结果均存入预先定义的专用寄存器udiv_remainder、overflow和div_by_0中。这些寄存器的使用由TIE代码进行描述。

iclass div_iclass {UDIV10x5} {out arr, in ars, in art}

{out div_by_0, out udiv_remainder,

out overflow}

指令行为描述

采用TIE语言可以描述UDIV10x5指令的实际操作,TIE语言与RTL的描述流程是一样的,只是在语法方面略有不同。尤其是TIEmux()模块(该模块例化一个多路器)代替了Verilog代码中的if-else语法,这种替换在逻辑综合时可以产生更加有效的处理器硬件。对UDIV10x5指令来说,完整的TIE描述需要的代码量不超过50行,同Verilog RTL的代码量基本相同。

软件工具的使用

Xtensa处理器产生器可以自动更新软件开发工具,以识别和仿真所有新添加的指令。不但如此,处理器产生器还能建立一个头文件(在此例中为udiv10x5.h),该文件包含C的内在函数(intrinsic),以便TIE指令可以被C程序调用。

结语

从概念上讲,通过处理器指令扩展来执行专用功能同RTL设计是非常相似的,但是它为SoC设计人员提供了更多独特的优点。对于当今的复杂算法来说,设计人员在构建SoC平台时通常会采用微处理器核来进行任务管理,同时必须设计定制的RTL逻辑,以获得高性能。如果通用微处理器不能令所有的任务执行都达到要求的性能,那么就需要用户定制硬件,而定制硬件必须要经过验证,会延误项目的开发周期。像Xtensa这样的可配置、可扩展处理器就能够解决这样的设计问题。

当然也可以将图1所示的RTL除法器设计成一个协处理器,并与通用处理器核相连。但是,由于微处理器核和协处理器之间存在着发送和接收数据的通信成本,因此这种设计方法的效率很低。TIE语言允许设计人员直接为Xtensa微处理器添加扩展指令,并将实现细节抽象化。通过为处理器核添加扩展指令,进而增加处理器功能,将新功能与微处理器相结合,消除了处理器核与协处理器之间的通信成本。

不仅如此,即使除法器模块本身设计不很困难时,微处理器核和协处理器之间的通信和接口验证也是一项很耗费时间的工作,尤其是需要对各种极端情况进行验证时。TIE语言以一种非常易于控制且非常有效的方式为处理器添加功能,并可以由Xtensa处理器产生器自动进行验证。从验证的观点来看,设计人员只需要验证扩展指令的行为(可由TIE语言进一步自动完成)。将新指令与Xtensa处理器结合的另一个好处是可以使用指令集仿真器ISS来验证程序代码,而不是采用速度较慢的RTL仿真器来验证RTL硬件协处理器。

通过TIE和Xtensa处理器产生器建立处理器扩展指令可以使固件程序员非常容易地添加新的指令。新指令可以像Xtensa处理器中的基本指令一样被调用,既不需要软件驱动程序,也不需要特殊的I/O代码。原来的软件可支持新的处理器指令,提高了应用程序的性能和灵活性。应用中的关键性能部分可以通过指令扩展来实现,软件实现的灵活性确保了高性能的系统设计。通过将需要的计算硬件封装到扩展指令中,这些与状态机相似的指令功能可以被转移到固件中,这就简化了SoC的硬件设计,同时允许在任意设计环节内(即使产品已经投入使用)对设计进行修改,以满足协议标准和市场需求的变化。