---无线设备在其发送通道和接收通道中需要用到数模转换器(DAC)和模数转换器(ADC),两者统称为数据转换器。过去,这些数据转换器通常直接连接到FPGA或者ASIC,再与通用DSP连接。这些DSP一般只提供连接到转换器的串行接口,根据音频应用的需要提供小于或等于1MSPS的采样速率。

---现在DSP的时钟频率可以高达300MHz甚至更高,所以DSP在需要高速采样的混合信号数据转换器的无线应用设备中可以取代FPGA和ASIC。带有直接存储器存取(DMA)的DSP允许外设和内存之间直接通信,而不必通过DSP内核。DSP的异步存储器接口通常可以被外部存储器和其他外设(例如LCD显示器和通信桥路)共享。

---然而,在每一个连续采样都至关重要的更高速的实时应用中,单独的DMA是不够的。因为DMA不是专门为连续的外部受控数据流设计的,所以它不适合直接连接到高速的ADC和DAC。而有些DSP(例如ADSP-BF532)的并行外设接口(PPI)能够满足这些高性能数据转换器的需求。 高速数据转换器的选择考虑

---一些特殊应用需求确定了高速数据转换器的性能限制和功能集合。例如,ADC可能需要宽输入带宽以支持直接中频(IF)输入信号的欠采样,而DAC可能会需要足够高的采样频率以简化对模拟滤波器的需要。选择一个高速数据转换器的其他考虑因素包括分辨率、动态范围、杂散性能、信噪比、信号幅度、易用性以及需要的带宽。

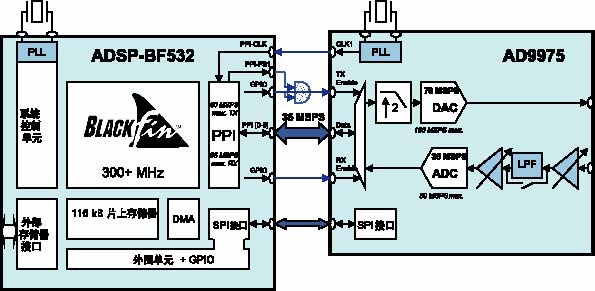

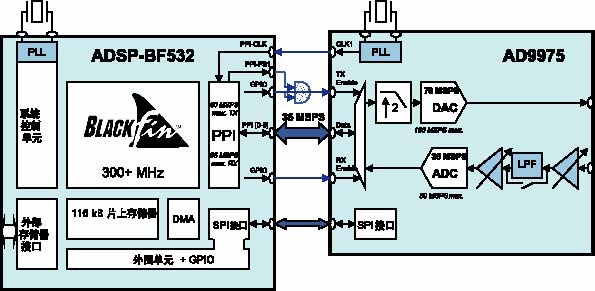

---在TDMA和半双工通信方案中发送和接收通道共享数据总线,所以这对于选择一个带有ADC和DAC功能的混合信号前端设备(例如MxFE混合信号前端)很有利。例如,AD9975是一种集成的单电源宽带调制解调器前端,它的发送通道包括一个内插滤波器和10位、50MSPS的ADC,其接收通道包括一个可编程增益放大器(PGA)、低通滤波器(LPF)和10位、50MSPS的ADC。这个集成的内插器非常重要,因为它允许以100MHz的频率采样发送信号,同时它保持数据总线带宽降至50MSPS,这种高采样频率显著降低了模拟重构滤波器的复杂程度。AD9975的特点如表1所示。

---高速数据转换器需要一个由外部振荡器产生的低抖动时钟。其内部锁相环(PLL)产生DAC内插采样频率。许多混合信号的数据转换器都提供一个额外的输出时钟直接驱动PPI的输入时钟。 并行端口接口

---并行端口接口(PPI)是一种可以配置成8位和16位之间宽度的多功能并行接口。它支持双向的数据流,并且包括三条同步信号线和一个连接到外部时钟的时钟引脚。该PPI能以高达65MHz的时钟频率接收数据。对于从PPI发送数据的应用,如果满足数据转换器的保持时间要求,其数据发送速率可能达到60MHz。该PPI还支持专用视频和通用并行数据应用,包括高速数据转换器的连通性。  DMA引擎

---虽然DSP的并行接口简化了其到高速数据转换器的连接,但这只是解决了部分问题。DSP还是必须先将数据存储在存储器中然后再处理它,并且将处理结果发送到某处(或者送入存储器或者通过某个外设输出)。这就是一个灵活的DMA引擎非常有用之处。

---首先,拥有不只一套存储器DMA通道是很重要的,以便能够同时支持多个存储器传送处理。例如,一条双向通道可能会支持SDRAM和内部存储器之间的原始数据块传送,而第二条通道可能将处理过的数据输出到异步存储器总线上的某个设备。再有,PPI有其自身独立的DMA通道,所以其性能不会因为存储器之间的数据传送而降低。

---另外,可编程DMA的优先级能够根据实时控制的原则保证外设要求的额外带宽能够达到它的要求。其次,“自动缓存”功能允许DMA当处理过程完成之后自动重新开始,所以使一个传送过程完成到下一个传送过程开始之间的等待时间非常短。

---有些DSP甚至提供“二维DMA”功能,这在无线系统中非常有用。这种功能主要允许将任意一个矩形区域的数据写入或者读出存储器。它还允许交叉存取,或者去交叉存取同相(I)和正交(Q)数据,或者视频图像中的亮度和色度分量数据的存取。  动态电源管理

---无线和便携式设备设计工程师在其研发初期必须考虑功率要求。幸运的是,如果选择DSP作为系统处理器,就不必再因为计算性能而牺牲功耗。为了提供一种实现便携式无线应用的最佳平台,DSP需要支持一种可以根据系统需求进行调整的多层次的电源管理方法。

---DSP内核的动态功耗与工作电压的平方成比例,还与工作频率成线性关系。也就是说,如果降低内核工作频率,会使其动态功耗呈线性降低,而如果降低内核工作电压会使其功耗呈指数降低。能够同时调整频率和电压的DSP,当它以较低的工作频率和较低的工作电压运行一段代码时能够节省许多电能。DSP必须能以最小的设计开销来处理电压-频率的变化。例如,当在ADSP-BF532中设置一种改动的时候,需要执行一个同步的电压和频率的变化。ADSP-BF532的特点如表2所示。

---当选择一个具有灵活电源管理的DSP时,要考虑的其他因素包括对多电源区域的支持、高度可编程的PLL、有选择地对禁止某些DSP单元电路的多种待机模式以支持最短周期有效。

---在数据转换器方面,典型的无线应用在发送数据脉冲串之前一直关断DAC的传输通道。旁路类似AD9975数据转换器中的有源接收滤波器和可编程增益放大器(PGA)也可以节省相当多的功率。当系统只是在等待检测数据脉冲串时,在空闲状态期间应该特别考虑降低功耗的接收工作模式。

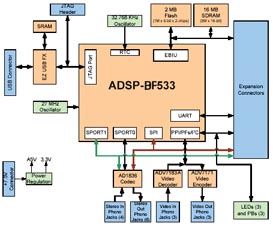

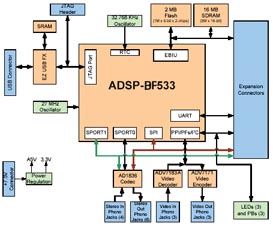

---对于带有并行外设接口(PPI)的DSP来说,将其与高速数据转换器相连是十分简单的。在混合信号宽带调制解调器前端的设计中,可将ADSP-BF532 Blackfin DSP的PPI做为一个35MSPS半双工接口和AD9975相连,电路如图1所示,ADSP-BF533评估板框图如图2所示。 系统数据流

---通过PPI实现DSP和数据转换器之间的物理连接是一种非常简单直接的方法。而且,实现这种接口只需要1个时钟和16个数据引脚。另外,当ADC和DAC共享这个接口时,通常采用一个接收允许信号。

---DSP中的串行外围接口直接连接到数据转换器的SPI端口以实现初始化、系统配置,控制增益、带宽和待机模式。

---在普通的TDMA和半双工无线应用中,基于DSP的收发器可能会频繁地在从ADC接收数据和通过DAC发送数据这两种状态之间进行切换。在PPI上进行不同操作方向(输入和输出)之间的切换时间只有几个系统时钟周期(一个典型的系统时钟速率是133MHz)。DAC操作可能会需要额外的保护,特别是利用共享的带宽,通过一个共享的媒介发送数据的时候。“清除”内插滤波器和其他清零的数据通道寄存器都能防止发送非预期的信号。当AD9975的发送允许信号被解除时,它自动地清除其数据通道寄存器。

---对大多数的应用来说,使用两个GPIO标志引脚直接控制混合信号前端数据转换器中的接收(Rx)允许和发送(Tx)信号是足够的。在这两个允许信号当中,只有一个信号在某一时刻能被启动,这取决于用户选择的是接收功能还是发送功能。

---系统设计工程师也可以利用PPI的同步功能精确安排一个发送数据脉冲串。在这种情况下,利用一个外部“与”门将发送信号和帧同步信号相“与”,其输出送给Tx允许引脚。

---将高速ADC和DAC直接连接到高性能DSP是可行的。较高的时钟速率、低功率和可直接连接数据转换器,这些特点使得DSP对便携式无线设备具有非常大的吸引力。 |