* ASIC芯片的设计周期在一年以上。在此期间,目标市场的通常会发生显著的变化;

* 有关标准,尤其是关于通信设备的标准迅速演进;

* 产品细分,尤其是从同一平台衍生出来的多种产品;

* 后继产品中的硬件重用。

在设计复杂的片上系统(SoC)时,设计者正在从ASIC方案转向在时间和资金资源方面更为经济的替代方案。Gartner Dataquest预测,在2002年到2007年间,ASIC销售综合年增长率将为8.4%。但Dataquest的ASIC、SoC和FPGA市场调查首席分析师Bryan Lewis指出,更为重要的是,以ASIC设计开始的项目数量将继续下滑,将会从1997年的11 000多下降到2006年的不足4000。与此形成鲜明对照,iSuppli的一项研究则预计FPGA市场将以更大的两位数年增长率持续增长:2003年为15.9%,2004年为25.6%,2005年则为26.4%。为进一步说明芯片设计领域向FPGA设计的转移,Hier Design的Jackson Kreiter,在2003年9月1日的EEdesign上的文章《为什么EDA不能忽视FPGA》中指出:“在2002年,有90 000个以FPGA开始的设计,与以ASIC开始的设计相比,其比率达到10:1以上。”

为减轻ASIC设计遭遇的困境,赛灵思公司(Xilinx)开发了一种新的FPGA架构,称为ASMBL,即面向特定领域应用的组合模块架构。使用这种新架构,用户就可以通过选取最佳特性和功能组合,快速且经济地实现面向多个专门领域的FPGA平台应用。

ASMBL是什么

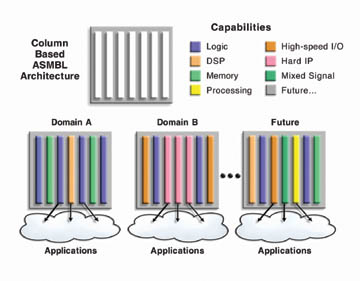

ASMBL通过使用独特的基于列的结构(见图1),实现了支持多专门领域应用平台的概念。每列代表一个具有专门功能的硅子系统,如逻辑资源、存储器、I/O、DSP、处理、硬IP和混合信号等。赛灵思公司通过组合不同功能列,组装成面向特定应用类别的专门领域FPGA(与专用不同,专门是指一项单一应用)。典型领域可能包括逻辑密集型、存储密集型或处理密集型领域。例如,用于图像处理的处理密集型芯片可能会含有较多的DSP专门功能列,而一个面向逻辑领域应用的芯片则不然。

ASMBL通过使用独特的基于列的结构(见图1),实现了支持多专门领域应用平台的概念。每列代表一个具有专门功能的硅子系统,如逻辑资源、存储器、I/O、DSP、处理、硬IP和混合信号等。赛灵思公司通过组合不同功能列,组装成面向特定应用类别的专门领域FPGA(与专用不同,专门是指一项单一应用)。典型领域可能包括逻辑密集型、存储密集型或处理密集型领域。例如,用于图像处理的处理密集型芯片可能会含有较多的DSP专门功能列,而一个面向逻辑领域应用的芯片则不然。

着重解决技术问题

ASMBL架构从两个级别对设计进行了提升,一是解决基于应用领域的设计问题,二是解决在传统ASIC和FPGA设计中都存在的一些技术约束问题。特别指出,ASMBL成功地缓解了与I/O和阵列相关性、电源和地分布,以及硬IP缩放相关的约束问题。

I/O和阵列相关性

传统芯片可分为两大类:内核约束型和I/O约束型。内核约束型芯片是指硅片尺寸受其内含逻辑数量制约的芯片。硅片周边长度远远超出在芯片四周部署I/O、时钟、电源和地焊盘必需的长度。焊盘约束型芯片的硅片尺寸则由其四周焊盘必需的长度决定,即使在遵守芯片设计规则的情况下使焊盘尽可能相互靠近,还是会存在芯片内部有浪费的未用区域[XAP1]。

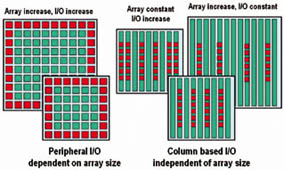

ASMBL的基于列的架构消除了同时困扰内核约束型和焊盘约束型设计的面积-周长相关性问题。图2的左侧显示,对于传统的焊盘约束型芯片,如果该设计需要容纳更多的I/O焊盘,就必须增大芯片尺寸。图2的右侧则显示,使用ASMBL架构的芯片,只需分配更多的列给I/O功能就可以容纳额外的I/O焊盘,而无需增加芯片的总体尺寸。由于芯片成本随硅片面积增加而上升,因此这种架构将极大地节省成本。与此类似,如果设计需要增加功能(内核)区域,也无需增加更多的I/O列就可以实现。

为了使基于列架构的I/O块能够放置在芯片周边以内,基于ASMBL的芯片采用了倒装芯片封装,这样就允许在芯片的任何位置放置焊盘,而不仅仅局限在芯片周边。倒装芯片技术就是将芯片在封装内“上下颠倒”再进行装配,微小焊球将各个焊盘(I/O、电源等)连接到内部封装互连。然后使用焊球技术将封装引脚连接到一块印刷电路板或其他基片上。除了允许在芯片内部放置焊盘以外,倒装封装还提供了比压线封装更强的散热能力。

为了使基于列架构的I/O块能够放置在芯片周边以内,基于ASMBL的芯片采用了倒装芯片封装,这样就允许在芯片的任何位置放置焊盘,而不仅仅局限在芯片周边。倒装芯片技术就是将芯片在封装内“上下颠倒”再进行装配,微小焊球将各个焊盘(I/O、电源等)连接到内部封装互连。然后使用焊球技术将封装引脚连接到一块印刷电路板或其他基片上。除了允许在芯片内部放置焊盘以外,倒装封装还提供了比压线封装更强的散热能力。

电源和地的扩展性

ASMBL架构还提高了FPGA中电源和地的分布能力。与把I/O焊盘放置在FPGA内部类似,设计者也可以将电源和地焊盘部署在在芯片内部的任意位置。Dataquest首席分析师Gary Smith在2002年10月的一篇市场趋势报告中表示,“电源已成为设计工程师面临的首要问题……”

随着工艺尺寸缩小,电源电压也随之降低。电源电压不断降低,片上时钟频率和数据速率日益提高,使得抑制产生的瞬时电压尖峰和接地反弹(Ground bounce)以满足芯片电源和信号完整性(SI)规范十分困难。为了克服这些问题,设计人员必须在芯片上增加额外的电源和地焊盘,以加强电源网络分布和减少片上寄生压降。相比于在传统芯片设计中设计人员只能在芯片的周边部署电源和地焊盘的情况,ASMBL对内部电源和地焊盘的支持极大地简化了均衡整个FPGA器件电源分布的任务。同时这还减小了电源下降、接地反弹和时钟畸变(因为时钟缓冲器分布在整个芯片上,故而可以得到更稳定的VDD电源电压和更均衡的接地),从而减小了片上信号完整性和信号延迟问题。

硬IP扩展性

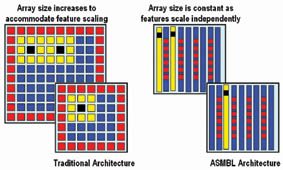

采用ASMBL架构的第三个优点就是该架构对硬硅IP缩放的支持。对于在传统FPGA架构中使用直线排列扩展IP核,向上扩展该核以容纳额外的特性可能会需要更大的FPGA(见图3)。在基于ASMBL的FPGA中缩放IP则只是意味着以列的方式增加更多IP,因此可以适合于已有的FPGA面积。这就有效地将IP缩放问题从二维(直线内核)降到一维(按列安排IP,缩放就可以通过增加IP列来完成)。因此,设计人员不必再为将硅IP核装入芯片而去寻求更大更贵的芯片。

使平台FPGA得到革命性改观

FPGA器件通过采用ASMBL及其列架构,利于开发针对专门领域的平台FPGA器件,而其价位点甚至比前代平台FPGA和平台ASIC及平台SoC还要低。通过使FPGA面向一个领域而不是一项专门应用,设计人员可以从选用已经具备为一定范围应用量身定制特性的器件来开始设计。设计人员可以对该器件编程,使其成为专门器件。这种组合给芯片带来多种不同级别的设计灵活性。

比之内部含有预定义硅IP和标准总线的掩膜可编程平台芯片——ASIC或SoC,ASMBL架构的这种灵活性和快速开发时间具有显著的成本和设计时间优势。无论是定制顶层金属层还是定制整个芯片,平台ASIC都要在制造时根据所需存储器、逻辑和I/O结构为适合一项专门应用定制。如果应用环境发生变化或是厂商为适用一种相关应用而请求修改器件,为集成和连接不同的IP核,该芯片都只能重新设计,并重新生成部分或全部掩膜层。这在设计时间和掩膜层成本两方面均代价不菲。

基于ASMBL的FPGA针对覆盖一类相似应用的领域进行了优化,这样设计人员就可以将一片FPGA用于多个应用。相对而言,改变应用较为简单,只要对器件重新编程就可做到,从而得以充分发挥FPGA所固有的应用适应性。因此,这种架构无论在客户进行平台FPGA开发、经济有效地进行针对不同应用的多平台开发,以及对新的市场需求快速做出响应方面,都具有时间短、风险低的优点。

[XAP1]由于存在这种相关性,以致于在传统的IC设计中很容易出现硅片周边区域有浪费或者内部区域有浪费。