| 超高速高精度模拟电路SOI上的5V互补SiGe BiCMOS技术 |

| TEXAS INSTRUMENTS Badih El-Kareh等 |

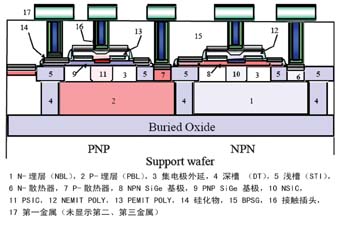

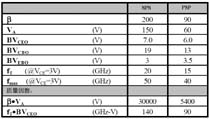

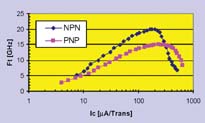

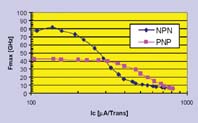

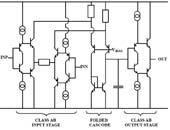

| 技术概览  ---第三代完全电介质绝缘的互补SiGe BiCMOS工艺(BiCom3)是针对超高速高精度模拟集成电路而设计的。上述器件的工作电压为5V,可在广泛的温度范围内工作,其fT的范围为15~20GHz,fmax的值在40~50GHz的范围,最小化了集电极到基板的寄生现象。fT的值反应出其性能比前一代互补技术提高了近三倍。 ---第三代完全电介质绝缘的互补SiGe BiCMOS工艺(BiCom3)是针对超高速高精度模拟集成电路而设计的。上述器件的工作电压为5V,可在广泛的温度范围内工作,其fT的范围为15~20GHz,fmax的值在40~50GHz的范围,最小化了集电极到基板的寄生现象。fT的值反应出其性能比前一代互补技术提高了近三倍。  此器件建立在商用SOI晶圆之上。首先定义掺杂浓度较大的p和n埋层。随后沉淀的是0.65μm的本征外延层,再加上填入氧化物的深、浅沟槽,尽可能减小寄生现象并提高电路密度。在确定双沟道(bipolar sinker)、CMOS阱与栅层叠后,采用新颖的dual-epi工艺来形成NPN和PNP SiGe双基极区。多发射极的尺寸极小,仅为0.4μm×0.8μm,采用独特的界面处理工艺形成。CMOS栅极、多晶硅高精度电阻和双基极多晶硅同时形成图案。在基极接触点上还采用CMOS源/漏极注入。在多晶硅底板上采用TiN顶板,由此形成MIM电容,并选择氧化电介质实现低电介质吸收效果。最后,将可用激光修整的NiCrAl薄膜电阻器集成到1.0μm间距的TLM后端,从而完成有关工艺。图1显示了最终的NPN和PNP器件的截面视图,表1总结了工艺流程。 此器件建立在商用SOI晶圆之上。首先定义掺杂浓度较大的p和n埋层。随后沉淀的是0.65μm的本征外延层,再加上填入氧化物的深、浅沟槽,尽可能减小寄生现象并提高电路密度。在确定双沟道(bipolar sinker)、CMOS阱与栅层叠后,采用新颖的dual-epi工艺来形成NPN和PNP SiGe双基极区。多发射极的尺寸极小,仅为0.4μm×0.8μm,采用独特的界面处理工艺形成。CMOS栅极、多晶硅高精度电阻和双基极多晶硅同时形成图案。在基极接触点上还采用CMOS源/漏极注入。在多晶硅底板上采用TiN顶板,由此形成MIM电容,并选择氧化电介质实现低电介质吸收效果。最后,将可用激光修整的NiCrAl薄膜电阻器集成到1.0μm间距的TLM后端,从而完成有关工艺。图1显示了最终的NPN和PNP器件的截面视图,表1总结了工艺流程。双极晶体管性能特点  该技术的主要组件为双极晶体管。对于使用互补设计的高性能模拟应用,使NPN与PNP的fT性能合理地匹配(因数在2以内)极为有效。除高fT之外,高速线性运算放大器已有其他信号调节电路也需要高晶体管增益,主要特点简而言之就是β·VA的积。增加VA通常以fT为代价,因为这需要提高基极的掺杂级,因而导致移动性降低,并增加了发射极电容。添加SiGe可以增强基场(field),从而抵消上述影响,这样在提高VA同时可得到更大的fT。表2给出了双极晶体管在室温下的特性。 该技术的主要组件为双极晶体管。对于使用互补设计的高性能模拟应用,使NPN与PNP的fT性能合理地匹配(因数在2以内)极为有效。除高fT之外,高速线性运算放大器已有其他信号调节电路也需要高晶体管增益,主要特点简而言之就是β·VA的积。增加VA通常以fT为代价,因为这需要提高基极的掺杂级,因而导致移动性降低,并增加了发射极电容。添加SiGe可以增强基场(field),从而抵消上述影响,这样在提高VA同时可得到更大的fT。表2给出了双极晶体管在室温下的特性。NPN与PNP的fT及fMAX曲线图分别在图2和图3中给出,这里的器件为0.4μm×0.8μm器件。  --- --- CMOS和无源组件 电路应用

结论 |