摘要 在设计商和制造商之间构建一种信息交流的平台可以提高产能和良率。

RET挑战

在新型EDA工具和流程的帮助下,设计人员正在准备将设计信息嵌入到制造数据中,从而可以采用后道加工工具对关键的设计结构进行优化分析。不过,新型的设计工具不断涌现,使设计人员可以运用更加有效的手段来满足后道光刻工艺的要求。对这些工具采用一套能够破解光刻限制的复杂的设计规则就可以在流片设计之前对有麻烦的结构进行识别和校正,这样就产生一种被称为“用光刻对设计加以确认”的新方法。

我们来分析一下现有的用光刻来确认的设计的各种流程和方法。所有的流程和方法都基于假设,通常会假设一种预测或校准的光刻模型相当精确,足以涵盖所有的设计变化。对模型进行微调和验证有时会需要数月的时间。在许多情况下,校准模型的精度是不够高的,通常只能满足一层和聚焦条件的要求。当前半导体工业界正在开发贯穿整个工艺过程的窗口模型,有了这种模型就可采用更为有效的“热点”探测方法。还有各种各样的方法可用于布局安排和寻找边缘可印区。

设计类型以及设计人员对目标的执着追求在决定是否应该对“热点”做更进一步的处理中起着至关重要的作用。对一种真正有效的由光刻来确认设计的方法而言,制造能力需要让设计人员了解。同样,设计人员的目的也必须与制造业的相关人员进行交流(图1)。等到流片设计好之后再发现与设计相关的问题就为时已晚矣,就迫不得已地需要采取冒险的方案了。更何况通常是无法发现这些问题的,因而相同的问题还会困扰后道工艺的设计人员。解决这类问题的一个方法就是,任凭这种不断对设计人员增加限制的趋势发展下去,从而使所制订的完整的设计流程为“白痴”方案。这样做的结果通常会造成设计规则手册越来越厚,而且还要不断地补充建议使用的DFM规则。虽然这种做法对某些产品有效,但它也会限制布局的的竞争能力,还会牺牲芯片的面积。

最终的结果是,所有的设计数据都必须利用一种或更多的模型最后通过某种RET处理和光刻模拟。在冗长的设计周斯中,这样做还有助于在这些变化还未造成经济影响的时候能尽早地发现工艺中的重大缺陷。与DRC相同,设计人员也十分希望在进行耗资更大的电学检验与模拟之前对设计布局加以验证。设计布局的任何改变都会迫使他们返回前道工艺重新检查整个操作过程。像信号的完整性、电迁移、CMP效应、寄生影响以及其它参数的模拟与测试只能在布局设计之后的固定条件下完成。光刻模拟也可能会十分耗时,且计算量会很密集,但任何事情都不可能不劳而获。使用任何捷径和诀窍总要在性能与精度之间打一些折扣。

热点实例

我们来检查一下可能会产生热点错误的根源,了解所涉及的各组的情况,并探讨便携式PMF为何能发挥重要作用:

第一组:光刻工艺与模型校准—可印刷的限制不仅是扫描仪波长的函数,而且还是许多物理效应的函数。这些物理效应在次分辨率节点会发挥作用。

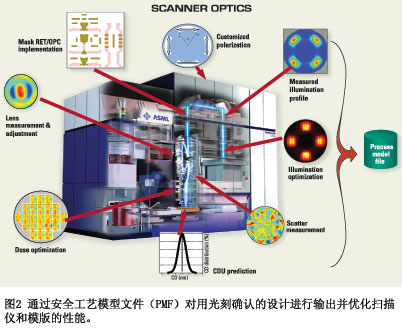

采用高级模拟工具即可对扫描仪和抗蚀剂工艺进行优化。此外,还可以对这些优越的特性进行控制,进而将其应用到PMF中。例如,除了1个或更多的校准模型之外还可以将测得的照明装置的分布情况附加到PMF中,并应用于诸多的后道模拟工具中(图2)。这样,设计链中的其它工程师即可有机会对校准模型无法提供的其它条件进行测试。

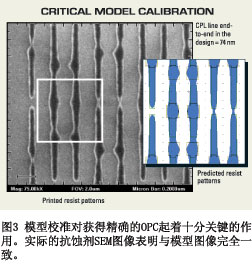

一旦模型得到校准(图3),就会表现为霍普金斯核的形式,否则这一信息就会丢失。PMF还能改善闭合环路反馈,使光刻工程师能很方便地将其现有的工艺简况传递给设计人员,这样设计人员就可以尝试各种测试图形或可印刷性布置。重要的是要认识到,各个研究组织中参与布局设计的工程师数量总是会超过光刻或集成工程师的数量。因此,采用所选择的最终光刻方法在大范围的预定厂房内进行快速重复的能力会极大地提高整个工艺的价值和性能,并可缩短理想工艺条件的形成周期。

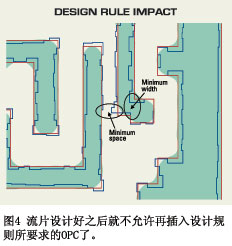

第二组 :设计规则— 在制订设计规则的初期阶段,需要快速地重复工艺变化,还要进行设计可行性研究。一旦相对固定,下一阶段就要制订希望布局设计人员遵守的设计规则。假设已对各种布局情况做出了全面分析,那么这些设计规则就会给出正常完成RET处理工艺所需要的适当的预算。这可能就意味着已具有足够的空间可用于提高边缘偏置的准确量或次分辨率加速特性。一些双曝光技术甚至可能会有额外的规则用于多角替换。为了在某些规则限制上给设计人员提供一些灵活性,经常会推出第二套DFM建议规则。这样设计人员就可以选择他或她自身的命运。在某些情况下,是不能为了推行建议使用的规则而牺牲布局设计的(图4)。

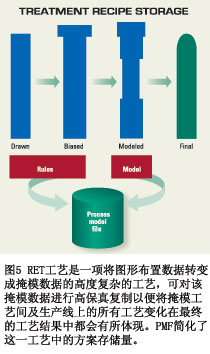

第三组:重新制订目标规则和模型OPC方案— RET工艺是一项将图形布置数据转变成掩模数据的高度复杂的工艺,可对该掩模数据进行高保真复制以便将掩模工艺间及生产线上的所有工艺变化在最终的晶圆结果中都 公有所体现。在这儿的第一种假设是,可对制造工艺的可变性进行精确的模拟,并将其运用到处理引擎中,对掩模数据进行准确的补尝。第二种假设是,设计规则已在布局中给出足够量的预算,可以补充所需的所有规则/模型基校正。为了加速模型基处理,经常要先采用规则基处理。这可能包括重新制订规则,重新制订规则时某种边缘结构可能会发生偏置。也许还要用到锤头和分散条。这样会使模型光学邻近效应校正(OPC)引擎上的负载得到一定的缓解,并起到加速结合的作用。OPC方案本身十分复杂,其呈几何结构状的引擎会将目标边缘分成多个小块,用于重复运动/评估循环。它与模拟引擎共同作用,利用光刻模型找到所有运动边缘的最佳安排。边缘分隔的块数越少性能提高的程度就会越大;然而,这是以牺牲精度为代价的。产生的小块越多,运行时间和文件量就会增加得越多(图5 )。

第四组:RET之后的校验装置—RET之后的数据校验计算工作量极其庞大。现在的标准做法是将大量的计算资源用于完成对掩模数据进行模拟和探测热点的复杂任务。在多个工艺窗口条件下,这相当于首先对模型的等值输出建立一条防护频带,然后再与目标层进行对比。因而当使用者发现有问题的区域时会面临着不知如何处置的巨大挑战。在这里要假设模型是可以信赖的,DRC是清洁的,OPC方案已完成其目标任务。现在发现一个热点,可同时问题就出现了,它产生的根源是什么呢?通常,需要采用SEM图像在与热点相同的位置上做一次全方位的检查,测定预测的准确与否。最后一种可能性是,RET校验工具的设置有点不合适,给出的报告是不真实的或者是过于悲观/不够悲观。

对所有的EDA供应商来说,如何处置限定区域内的问题仍然是一个重大的挑战。每一个设计流程可能会与其它设计流程有着明显的区别,因而也有着不同的要求。将热点改到流程中的适当点上以便于纠正也正是拥有PMF的价值所在。然后即可利用PMF的特点采用1-4组的工具设置对讨厌的数据进行分析。

集成方法

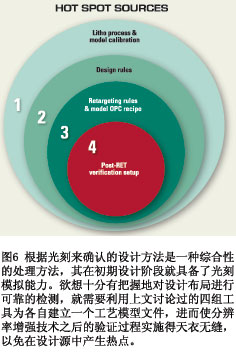

由光刻确定设计的方法是一种综合的处理方法,在初期设计阶段它即具备了光刻模拟能力。欲想十分有把握地对设计布局进行可靠的检测,就需要利用上文讨论过的四组工具为各自建立一个工艺模型文件,进而使分辨率增强技术之后的验证过程实施得天衣无缝(图6)。验证得出的结果只具有和处理等同级别的精确度,而处理是在设计规则的范围内进行考量的。最后,设计规则也在光刻工艺的限度内,而这个光刻工艺已根据模型进行了校准。

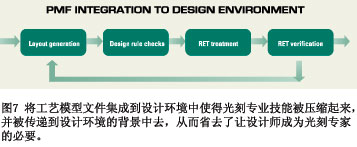

将工艺模型文件集成起来编入预流片设计阶段-或者是设计环境-正是它的价值所在(图7)。将集成方法应用于由光刻来确定设计做法具有特别的重要价值,因为设计纠正的费用一直在不断上涨。每一个设计人员都想第一次就做出正确的设计。在流片设计之后对热点进行修改的能力一般不会有问题,除非你在实际的布局、设计规则、或者是光刻工艺过程中发现了需要纠正的问题的时候遇到麻烦。

结论

没有人会否认,设计业和制造业之间需要进行更加有效的沟通。实际上,当我们离更为先进的工艺节点越来越近时,这种沟通就显得十分有必需。在这篇文章中,我们对一种基本的平台进行了介绍,正是因为有了这种平台才使密切的沟通和交流成为可能,同时还优化了设计与制造业之间的界面。

我们应当把工艺模型文件看作是一种切实可行的技术。它是一项基本平台,利用这一基本平台,关键的模型和设计方案信息即可以自由的上传或下传。有了这种交流通道就可以使新技术节点以更高的速度直线增长,而且还能使设计一次成功。工艺模型文件本身就可以保护其内容不至于外泄,同时还允许设计师执行并察看安全开关设置所支配的最终结果。这些结果能以一整套信息的形式发送给设计师,并且这一套信息具有与DRC相类似的外观和感觉。还可延伸其性能以支持其他类型的工艺,包括CMP, 蚀刻技术以及粒子分析模型等(图8)。