vfdff

vfdff

vfdff发表的帖子

[讨论]为何if rising(clk) 内部和外部赋值有不同效果??

[讨论]为何if rising(clk) 内部和外部赋值有不同效果??

process(clk,R4_en) -- 5。24 需要修改使只有在一个 R4_en 高电平的时候启动(修改前)

constant dalay_clk : integer := 2 ;

variable count : integer range 0 to 7 := 0;

begin -- 有没有 and R4_en'last_value='0',效果一样!

if(clk'event and clk = '1') then

G0 <= G0_tmp; -- 很奇怪,为何 G1,G2需要整体再乘以一个 i,把虚实部交换

G1 <= (NOT G1_tmp(WORD_WIDTH/2-1 downto 0)) & G1_tmp(WORD_WIDTH-1 downto WORD_WIDTH/2);

G2 <= G2_tmp;

G3 <=(NOT G3_tmp(WORD_WIDTH/2-1 downto 0)) & G3_tmp(WORD_WIDTH-1 downto WORD_WIDTH/2);

if(R4_en='1')then

if(count = 0) then -- 只在记完三个周期的时候或者刚进入使能有效的时候开启记数

AA <= A; BB <= B; CC <= C; DD <= D; -- 保证只在 R4_en='1'时开启运算

count := 1; -- 在高电平之后启动记数

elsif(count> =dalay_clk and R4_en='1') then -- 达到第 三 个时钟,运算完成

R4_end <= '1'; -- 运算完成后输出高电平

elsif(count> 0 and count <dalay_clk and R4_en='1') then -- count> 0 表示已经接收到R4_en='1'

count := count + 1; -- 在记数状态(R4_en='1'),且时钟未到

end if; -- count

else

R4_end <= '0';

count := 0;

end if;

end if; -- R4_en

end process;

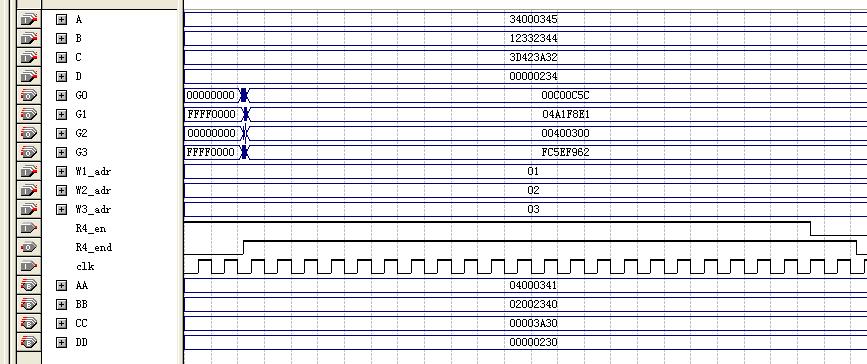

上面程序中复值后波形仿真发现 AA = A; BB = B; CC = C; DD = D; 不成立,怎么办??

好象是没有完全复值,因为是基本上一致,就某些位上不一致!!如图: 此主题相关图片如下:

此主题相关图片如下:

发表时间:2007年5月26日12:44:32

回复该帖

本主题共有 1 帖,分页:>>>>>该主题的所有内容[1]条

[上一篇帖子]:老古:求救!!ISA采集卡的采集程序C编写老古,你好!我是位新人! 最近在忙毕业设计,用C

[下一篇帖子]:quartus 软件仿真怪事 /P P 今天发现一个很大的问题,我程序中的逻辑和qua

导航:

导航: