vfdff

vfdff

vfdff发表的帖子

quartus 软件仿真怪事

quartus 软件仿真怪事

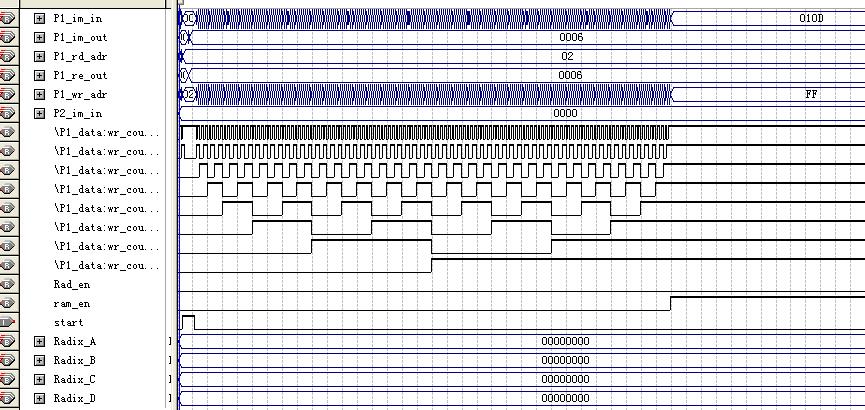

今天发现一个很大的问题,我程序中的逻辑和quartus 编译器波形仿真图刚好相反,向老师请教了下,他看了下说偶然有这种情况是正常的,但是我一连编译了很多次,拨行图一直这样反着,难道某种格式她句容易看反了吗??

我以前用着一直没有问题的,今天郁闷了!!

程序如下,附件为波形图,希望哪位用别的仿真器帮我看看效果是不是一样的??

主要是 start 和 ram_en 的两个波形有问题(和程序对照看)

P1_data:process(clk,start,Radix_fb)

variable wr_count :std_logic_vector(7 downto 0):= (others=> '0');

begin

if(start='1') then -- 高电平初始化

ram_en <='1';ram_wr_en <='1';wr_count := (others=> '0'); -- 第一阶段

finish <= '0';

elsif(Radix_fb='1' and ram_en='0') then -- 第二阶段反馈,即进入第三阶段

ram_en <='1';ram_wr_en <='0';wr_count := (others=> '0'); -- 第三阶段

finish <= '1'; -- 高电平时接收到数据为正确的结果

else

if(clk'event and clk='1' and ram_en='1') then -- 在一、三阶段

if(wr_count="11111111")then

if ram_wr_en='1' then -- 第一阶段

P1_wr_adr <= wr_count;

P1_re_in <= re_in;P1_im_in <= re_in;-- 从数据线上接收数据

ram_en <='0'; -- 进入第二阶段

else

P1_rd_adr <= wr_count;

re_out <= P1_re_out;im_out <= P1_im_out;-- 把结果送回数据线

end if;

finish <='0';

else

if ram_wr_en='1' then

P1_wr_adr <= wr_count;

P1_re_in <= re_in;P1_im_in <= re_in;

else

P1_rd_adr <= wr_count;

re_out <= P1_re_out;im_out <= P1_im_out;

end if;

wr_count := wr_count+'1';

end if; -- wr_count

end if; -- clk

end if; -- start

end process P1_data;

此主题相关图片如下:

此主题相关图片如下:

发表时间:2007年5月26日12:41:46

回复该帖

本主题共有 1 帖,分页:>>>>>该主题的所有内容[1]条

导航:

导航: