摘 要:工艺设计工具包PDK在数模混合信号/射频电路设计中应用广泛。本文简要介绍了PDK的应用,并说明了如何使用 Cadence的自动化开发系统PAS 去开发PDK。

关键词:PDK;PAS;Pcell;GTE

引言

随着混合信号设计复杂性的日趋增加,开发PDK(Process Design Kit)并建立验证参考流程对于降低昂贵的设计反复所带来的市场风险是非常重要的。一般来说,晶圆厂会根据工艺技术的要求定制PDK的设计组件,每个工艺都会有一套对应的PDK。本文介绍的PDK结合了晶圆厂的先进工艺技术以及Cadence公司Virtuoso平台的模拟/混合信号设计方案,使得混合信号的芯片设计工程师能够将更多的功能集成到一块芯片上。

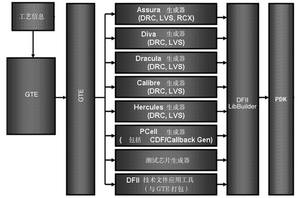

图1 PDK的设计应用环境

图2 PDK的开发流程

PDK的应用

工艺设计工具包PDK是为模拟/混合信号IC电路设计而提供的完整工艺文件集合,是连接IC设计和IC工艺制造的数据平台。基于Cadence全定制IC设计流程的PDK提供了完整的解决方案,能够实现IC工艺数据/模型与IC设计环境/工具的无缝集成,缩短设计周期,并提高设计产能和效率。

PDK是面向特定工艺的的设计包,支持的IC工艺包括CMOS、双极、BiCMOS、SOI和GaAs。

PDK应用于混合信号设计,其包含的内容是和全定制流程紧密结合在一起的。图1很好地说明了PDK和设计流程及设计工具之间的关系。如图1所示,除PDK的参考手册(Documentation)外,PDK的内容还包括:

器件模型(Device Model):由Foundry提供的仿真模型文件;

Symbols & View:用于原理图设计的符号,参数化的设计单元都通过了SPICE 仿真的验证;

CDF(Component Description Format,组件描述格式) & Callback:器件的属性描述文件,定义了器件类型、器件名称、器件参数及参数调用关系函数集Callback、器件模型、器件的各种视图格式等;

Pcell(Parameterized Cell,参数化单元):它由Cadence的SKILL语言编写,其对应的版图通过了DRC和LVS验证,方便设计人员进行Schematic Driven Layout(原理图驱动的版图)设计流程;

技术文件(Technology File):用于版图设计和验证的工艺文件,包含GDSII的设计数据层和工艺层的映射关系定义、设计数据层的属性定义、在线设计规则、电气规则、显示色彩定义和图形格式定义等;

PV Rule(物理验证规则)文件:包含版图验证文件DRC/LVS/RC提取,支持Cadence的Diva、Dracula、Assura等。

PDK的开发

由晶圆厂提供的工艺信息,包括了设计规则文件、电学规则文件、版图层次定义文件、SPICE仿真模型、器件版图和器件定制参数。如图2所示,晶圆厂提供的工艺信息是开发PDK唯一的输入条件,利用它们在PAS(PDK Automation System)中开发GTE(Graphical Technology Editor,图形化技术编辑器)的数据集,即可生成PDK的各种工具包。

技术文件

在PAS GTE中,技术文件中的层次定义方法是和Virtuoso版图编辑器一致的。在技术文件和显示文件都已经存在的情况下,就可以把这些文件直接输入到PAS GTE中。

PV Rule文件

PAS GTE 可以让用户用图形化的方式定制与DRC/LVS/RCX文件有关的工艺技术信息。然后通过PAS GTE生成器生成PV文件,用户可以根据需要生成各种PV工具支持的文件格式。这些文件不仅能够支持Cadence 的Assura、Dracula和Diva,而且还能支持Mentor Calibre和Synopsys Hercules。它在PV文件的维护方面保证了数据的一致性,因此,用户不必为了维护不同的PV文件而付出大量的努力。特别地,晶圆厂需要开发和维护大量的PV文件以支持不同的设计平台,对它们来说,这种方法是非常有效的。

Pcell和CDF&Callback

Pcell是参数化的单元,这里的参数指的就是CDF参数。它们的组合能够实现用户定制的所有功能,是PDK的核心部分。

PDK的Pcell和CDF&Callback都是由SKILL语言开发的。SKILL编程语言可以定制并扩展用户的设计环境。它提供了一种安全和高级的编程环境,能自动处理很多传统的系统编程操作,如存储器管理。SKILL语言也能在Cadence的工具环境中被立即执行。更重要的是,它允许用户访问和控制所有工具环境中的组件,如用户接口管理系统,设计数据库和设计工具的命令库。

Pcell是可编程的单元,可以让用户创建定制器件。其实,PDK的库就是指所有Pcell的合集。用户创建的Pcell可以被称为一个Master,由图形化版图和参数组成。当编译这个Master之后,它就以SKILL程序的形式存储在数据库中。当调用版图时,参数会被赋予指定的值,或使用缺省值。

Pcell可以加速插入版图的数据,避免了单元的重复创建;它节省了物理磁盘的空间,相似部分可以被连接到相同的资源;它避免了因为要维护相同单元的多个版本而发生的错误;它实现了层级的编辑功能,不需要为了改变版图的设计而去改变层级结构。

CDF能够描述器件的参数及参数属性,让用户创建和描述定制器件。一些CDF还带有强大的Callback的功能,当某些参数改变时就会执行和它有关的Callback。比如,在用户需要根据电阻的宽、长和方块阻值来计算其阻值的时候,就可以应用Callback来实现复杂等式的计算功能。

Library Builder

PAS的Library Builder能把开发的GTE数据自动生成一套完整的PDK,也就是说Library Builder会运行上面所有的GTE生成器来建立PDK库,它包含了Pcell、CDF&Callback、PV文件、技术文件、器件模型文件和Symbol。生成的PDK库可以直接给用户使用。

结语

Cadence开发的PDK将设计人员、EDA设计工具、工艺制程紧密结合,简化了越来越复杂的混合信号设计,加快了产品的面世速度。对于混合信号、模拟或射频的芯片设计,尤其是对上市时间要求比较严格的设计,如果拥有了经过验证的Pcell结构、符号及规则等优化集合的PDK, IC设计人员的工作就能从繁琐易错的任务中解脱出来而变得高质量且富有效率。