摘要 在DRAM电容(capacitor)形成COB的工艺中,出现了表面粗糙多晶硅(rugged poly)的表皮剥落(peeling)现象。 这些剥落的表皮会在随后的工艺中转移到晶圆正面的中心部位,从而导致大约10%的良率(yield)损失。经过多次实验,解决方案是对晶圆背面进行多晶硅腐蚀(backside poly etch)。

湿法化学腐蚀技术从它出现时起,就一直应用于半导体制造领域。单晶圆湿法腐蚀工艺技术的设备和化学品的创新和改良给传统的湿法化学腐蚀技术带来了新的生命和新的工艺应用[1]。晶圆背面腐蚀就是其中之一。最近又发展了很多新的工艺应用,包括多晶硅的晶圆背面腐蚀,这些工艺的目的大多是为了是避免不同工艺之间的交叉污染(cross contamination)以及防止由于多晶硅薄膜的淀积而滞留的微量气体造成随后的真空工艺的气体污染(outgasing)[2]。本文将介绍多晶硅的晶圆背面腐蚀新的应用,即用来改善晶圆的微尘颗粒水平从而提高产品的良率。

粗糙多晶硅简介 在DRAM工艺中,单元的电容是非常重要的参数,它直接影响到元件的能量消耗。我们知道,

C=kA/d

其中: C: 单元的电容

k: 绝缘常数

A: 电极表面积

d: 电介质厚度

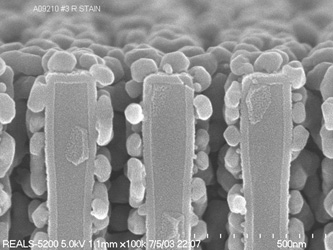

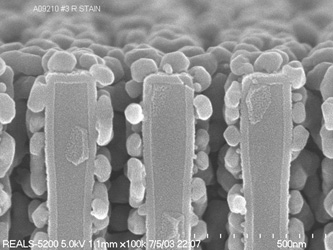

所以,如果电介质材料不变(通常是氮化硅和氧化硅),通过增大电极的表面积是一个重要的途径可以用来增大单元的电容。表面粗糙多晶硅(rugged poly)就经常被用做来增大电极的表面面积的目的。图1是表面粗糙多晶硅电容元件的剖面图。

图1. 表面粗糙多晶硅电容元件的剖面图

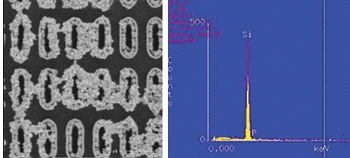

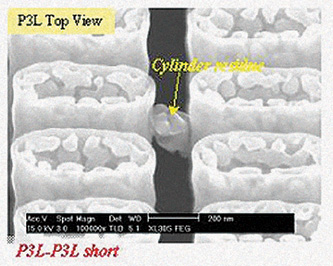

在表面粗糙多晶硅的沉积工艺中,晶圆的正面和背面都会有粗糙多晶硅的沉积。而这些沉积在表面的粗糙多晶硅因为生长方式的原因,通常比较容易剥落。在表面粗糙多晶硅的沉积工艺步骤之后到上电极板沉积的工艺步骤之前,还有很多工艺步骤,比如化学机械研磨或湿法清洗工艺。在这些工艺中,附着得比较弱的粗糙多晶硅,或晶圆边缘等容易产生应力的地方的粗糙多晶硅很容易从表面脱落。并造成晶圆表面大量的颗粒缺陷(图2)。这种大量随机分布的多晶硅颗粒会造成电容之间的短路(图3)并导致将近10%的良率损失。应用晶圆背面的多晶硅腐蚀工艺,可以针对这一失效做出很大的改善。

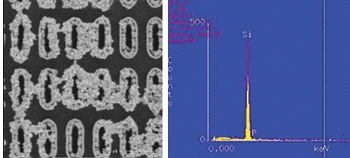

图2.晶圆表面的颗粒缺陷,成分是硅

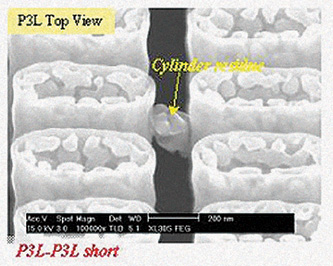

图3.剥落在电容之间的多晶硅颗粒

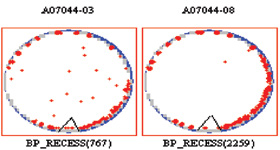

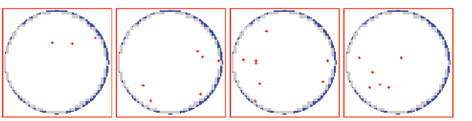

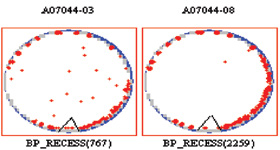

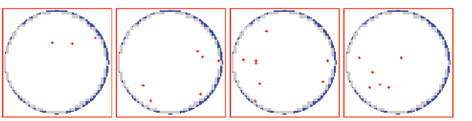

最早的多晶硅剥落现象能在“BPSG凹陷”工艺之后被发现。这个工艺是将所有的包在电容外边的BPSG薄膜腐蚀掉,从而增加电容的表面积。图4 是这步工艺之后的晶圆表面缺陷分布图,可以作为此类缺陷的参照图。在电子显微镜下面看到的此类缺陷可以参照图2。这类缺陷很难被湿法清洗工艺去除,并会在随后的工艺中,例如电介质层的沉积工艺和上电极板的沉积工艺,转移并大量随机分布在晶圆的正面。为了防止在“BPSG凹陷”工艺中的多晶硅剥落,晶圆背面和侧面的多晶硅要先被腐蚀掉。图5 是应用了多晶硅的晶圆背面腐蚀后并进行了“BPSG凹陷“工艺之后的晶圆表面缺陷分布图。显然,多晶硅剥落现象已经得到了极大的改善。

图4.“BPSG凹陷“工艺之后晶圆表面缺陷分布图

图5. 应用了多晶硅的晶圆背面腐蚀在“BPSG凹陷“工艺之后的晶圆表面缺陷分布图

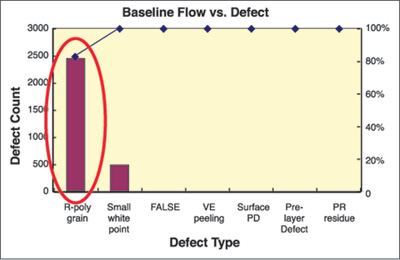

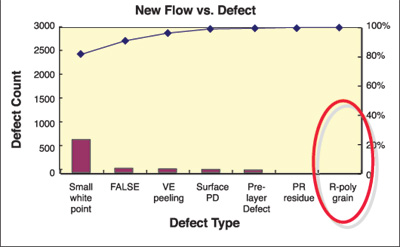

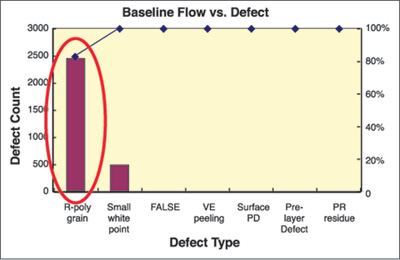

图6. 没有做晶圆背面腐蚀的,在上电极板沉积工艺之后的晶圆表面缺陷分类图

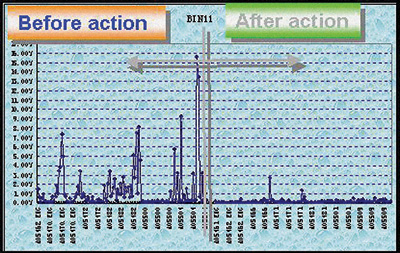

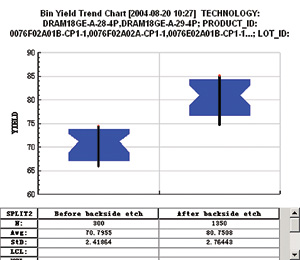

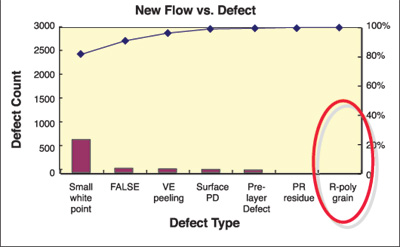

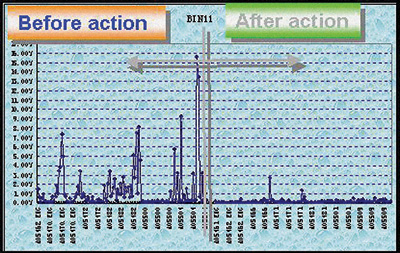

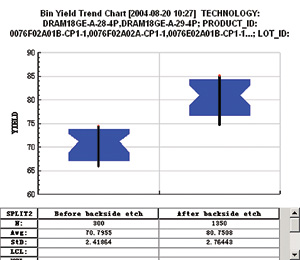

图6和图7显示了应用多晶硅的晶圆背面腐蚀工艺后,晶圆背面和侧面多晶硅颗粒剥落的状况得到了根本的改善。Bin失效也改善了很多(图8)。产品良率大约提高了10%(图9)。

图7. 做了晶圆背面腐蚀的,在上电极板沉积工艺之后的晶圆表面缺陷分类图

图8. 无晶圆背面腐蚀和有晶圆背面腐蚀的失效对比

图9. 无晶圆背面腐蚀和有晶圆背面腐蚀的良率对比

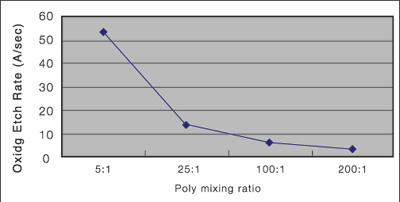

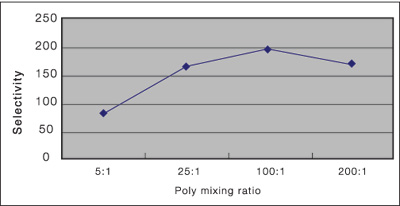

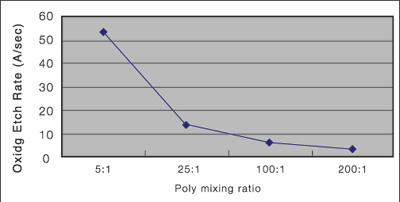

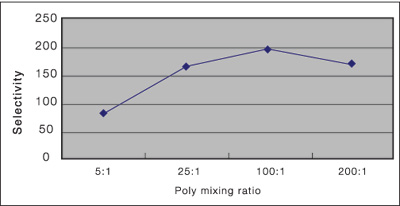

根据图10和图11的数据,晶圆背面的多晶硅腐蚀的工艺选用了100:1 HNO3/HF的配酸比率,并得到了很好的结果。

图10.氧化硅的腐蚀速率和腐蚀液混合比率的关系图

图11. 腐蚀率选择比(多晶硅对氧化硅)和腐蚀液混合比率的关系图

1. DRAM工艺中,晶圆背面或侧面的表面粗糙多晶硅容易剥落并导致大约10%的良率损失。

2. 晶圆背面的多晶硅腐蚀工艺可以很好地改善表面粗糙多晶硅剥落造成的表面颗粒缺陷。

参考文献:

[1] Harald Sax, Polysilicon Overfill Etch Back Using Wet Chemical Spin-process Technology. www.sez.com

[2] Hans Kruwinus. Backside Film Removal and It''s Impact on Semiconductor Production. www.sez.com

来源:半导体国际 作者:常延武,罗仕洲中芯国际集成电路制造(上海)有限公司 时间:2005/2/24 0:00:00