MathWorks 近日宣布推出 HDL Coder,该产品 支持MATLAB 自动生成 HDL 代码,允许工程师利用广泛应用的 MATLAB 语言实现 FPGA 和 ASIC 设计。MathWorks 还宣布推出了 HDL Verifier,该产品包含用于测试 FPGA 和 ASIC 设计的 FPGA 硬件在环功能。有了这两个产品,MathWorks 现在可提供利用 MATLAB 和 Simulink 进行 HDL 代码生成和验证的能力。

MathWorks 嵌入式应用程序和认证部经理 Tom Erkkinen 说:“世界各地的工程师都在使用 MATLAB 和 Simulink 来设计系统和算法。现在,有了 HDL Coder 和 HDL Verifier,他们在开发 FPGA 和 ASIC 设计时再也不用手动编写 HDL 代码,也不再需要手写HDL测试平台了。”

HDL Coder 利用 MATLAB 功能和 Simulink 模型生成可移植和可综合的 VHDL 和 Verilog 代码,可用于 FPGA 编程或 ASIC 原型开发和设计。因此,工程师队伍现在可以立即识别出针对硬件实现的最佳算法。Simulink 模型和所生成 HDL 代码之间的可追溯性同时也支持开发遵循 DO-254 和其他标准的高完整性应用程序。

Xilinx 全球营销和业务发展部高级副总裁 Vin Ratford说:“HDL Coder 提供与 Xilinx ISE 设计套件的集成通道,创建了一种按钮式工作流程,这样,使用 MathWorks 产品的算法开发人员开发面向 Xilinx FPGA 的应用就更加容易了。这种集成化使得我们的共同客户能够访问大量经过Xilinx优化的IP组合,进一步提高了他们的生产率。”

HDL Verifier 目前支持 Altera 和 Xilinx FPGA 开发板的 FPGA 硬件在环验证。HDL Verifier 提供协同仿真界面,能将 MATLAB 和 Simulink 与 Cadence Incisive、Mentor Graphics ModelSim 以及 Questa HDL 等仿真程序联结。有了这些功能,工程师可以迅速验证 HDL 实现是否符合 MATLAB 算法和 Simulink 系统规格。

Altera 公司产品及企业营销副总裁 Vince Hu 指出:“随着越来越多的行业采用 FPGA,

设计师需要一种方法来弥合系统模型和 FPGA 设计之间的验证差距。HDL Verifier 将系统模型与 FPGA 结合一起,使得工程师能够使用 Altera FPGA 和 Simulink 进行 FPGA 硬件在环验证。这个工作流程缩短了验证周期,同时也帮助工程师在芯片实现方面树立了更强的信心。”

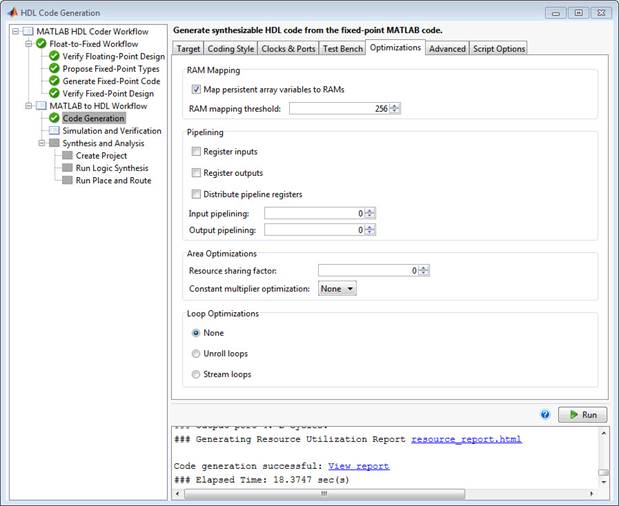

HDL Coder:HDL Workflow Advisor 提供自定义和优化 HDL 代码的选项,并能直接从 MATLAB 中自动进行 FPGA 编程。