图4 VIN .=20V时的栅阶电压

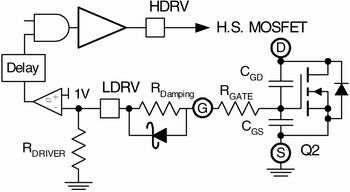

图6 肖特基二极管可降低阻尼电阻对自适应栅极驱动的影响,减少同步降压调节器中的短路现象

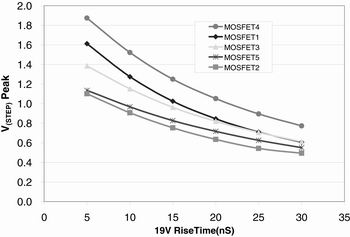

图8 在VIN=19V,SW在VGS(Q2) = 0.5V时开始上升, SW节点上升时间对于VSTEP 的影响

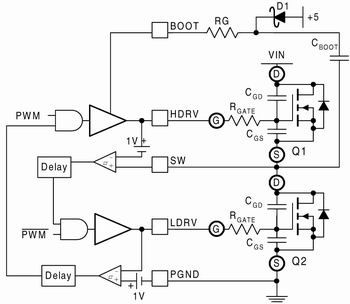

短路 (Shoot-through) 是指两个MOSFET同时完全或部分导通时,VIN至GND间有短路电流通过的情况。为了将短路减至最少,同步降压调节器IC通常采用以下两种方法来确保Q1和Q2按照“先开后合”的步骤操作,以减少短路的情况。

固定“死区时间”: 一个MOSFET断开,在一个固定的延迟时间之后,低边MOSFET才导通。这种电路比较简单,而且通常有效,但如果栅极电容值范围大的MOSFET配合给定的控制器应用,则缺乏灵活性。死区时间太长意味着传导损耗将会很高,但停滞时间太短则会造成短路。固定的死区时间往往会太长,因为它要让高Cgs值的MOSFET在配对的MOSFET导通前,将Cgs完全放电(断开)。

自适应栅极驱动: 这种电路根据MOSFET的Vgs被关断来确定何时导通配对的MOSFET。理论上,自适应栅极驱动电路可以针对给定的MOSFET产生最短的死区时间,而不会出现短路现象。

在实际应用中,自适应和固定死区时间方法的综合采用会达到最佳效果,图2所示的PWM控制器和栅极驱动器便是这样。

尽管这明显是由控制器进行的“先开后合”动作,由于栅阶(Gate Step)电压的存在,当高边MOSFET导通时仍会出现短路情况。

短路极难直接测量。短路电流仅持续几纳秒的时间,因此电流探测器中的附加电感会对短路波形造成很大影响。短路通常表现为振荡加剧、效率降低、MOSFET温度(尤其是Q1)升高及EMI增大。本文将提供预测短路的分析技巧和减少短路的方法。

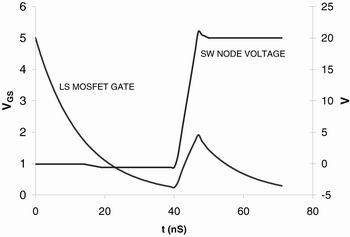

“栅阶电压”—短路的主因

如果自适应电路生效,就不会发生短路现象,此说法不确切。大部分短路是在高边MOSFET导通时发生的。SW节点(低边MOSFET的漏极)处的高dv/dt值通过Cgd耦合电荷,从而在驱动器试图保持栅极低压的极短时间内使栅极为正。Cgd和Cgs形成电容分压器,削弱了栅阶信号,因而在最坏的情况下,栅阶电压(VSTEP)的峰值振幅为:

考虑下面的情况

RDRIVER=2W,RDRIVER=1.2W

RDRIVER=5W

当自适应栅极电路切换时,内部MOSFET栅极电压为:

或在本例中为2.1V,有着显着的改善。

此外,肖特基二极管还减少了短路的持续时间,因为只有RGATE + RDRIVER释放CGS,而不是RGATE + RDAMPING + RDRIVER的总和。

表1所示为本例中采用和未采用肖特基二极管时的性能提升。

条件: 典型的低边MOSFET,由比较器感应至SW节点开始升压的延迟时间为25ns,19VIN,SW节点升压时间为10ns。

MOSFET的选择

MOSFET的特性对于栅阶电压产生短路电流的大小具有重要的影响。最坏的短路情况是漏极节点处的上升时间无限快(上升时间为0)。栅阶电压的大小很大程度上由CGS 和CGD 的相对量决定。一旦栅阶电压的大小确定(式(1)),短路电流的峰值就可以由下式计算得到:

表2所列为确定最大短路电流所需的相关MOSFET特性参数。

上表描述的每种MOSFET均采用不同的工艺,具有不同的内部电容比。

表3假定当HDRV导通时,VGS 已在SW节点升压前降至0。正如上表中所示,VSTEP 的最小幅值出现在MOSFET2和MOSFET5中,这两种器件均为低阈值器件。较大器件的阈值低是由于其栅极氧化层薄,使MOSFET具有很高的 (3)

(3)

式(3)中TR为MOSFET的上升时间。设计人员希望实现极快的上升时间(在SW上实现高值)来降低高边的功率损耗,但如果这种情况导致栅阶电压增大,造成短路,结果会比减慢上升时间所产生的损耗更大。在某些情况下,这是唯一能消除短路现象的实用方法。

如图8所示,减慢上升时间会对耦合到低边MOSFET栅极的VSTEP产生明显影响。TR减慢有助于降低EMI,但也会造成效率损耗。图8和表4所示为应用于笔记本电脑(双路并行)的输出电流为15A和19VIN的典型MOSFET的模拟运作。图8假定SW节点在内部栅极节点放电降至0.5V时开始上升。

表4 给出各个MOSFET由于短路造成的功率损耗。在Q1导通时开关损耗的主要为: (3)

(3)

表4最右一栏列出IOUT = 15A时,各个MOSFET上升时间的计算结果。

在大多数情况下,短路只是微不足道的问题,因此减慢高边上升时间并不是较好的选择,因为减慢上升时间造成的功率损耗会比消除短路所