摘 要:文中论述了集成电路技术向系统芯片(SOC)方向发展的必然趋势,以及在SOC时代EDA技术的几个重要发展方向和EDA工具的发展趋势。

关键词:集成电路;SOC;EDA工具引 言集成电路的发展已有40年的历史,它一直遵循摩尔所指示的规律推进,现已进入深亚微米阶段。由于信息市场的需求和微电子自身的发展,引发了以微细加工(集成电路特征尺寸不断缩小)为主要特征的多种工艺集成技术和面向应用的系统级芯片的发展。随着半导体产业进入超深亚微米乃至纳米加工时代,在单一集成电路芯片上就可以实现一个复杂的电子系统,诸如手机芯片、数字电视芯片、DVD芯片等。在未来几年内,上亿个晶体管、几千万个逻辑门都可望在单一芯片上实现。将整个电子系统集成在同一芯片上,称为片上系统(SystemOn Chip,SOC),或称为系统芯片。关于SOC的定义,许多专家从不同侧面提出了不同的定义。有一种定义为:在同一个芯片上集成了控制部件(微处理器、存储器)和执行部件(I/O接口、微型开关、微机械),能够自成体系、独立工作的芯片称为系统芯片。数字系统芯片一般都包含三大基本要素:处理器、存储器和接口逻辑。集成了这三类电路也就相当于在单个芯片上实现了数字系统的所有功能。

SOC是集成电路发展的必然趋势

技术发展的必然

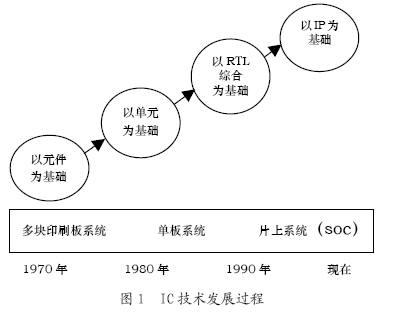

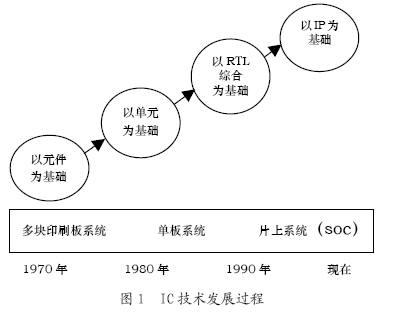

IC发展的初期,设计是从物理版图入手,以元件级为基础。随后出现单元库(Cell-Lib),设计从逻辑级开始,以单元库为基础,规模也随着增大。但由于单元库中的单元较小,因此设计效率较低。由于计算机、通信、多媒体的加速融合,对系统规模、性能、产品生命周期等提出了愈来愈高的要求,推动着设计技术和设计工具的改变,出现了以IP(IntellectuaLProperty,知识产权)为基础的片上系统集成。这种IP库与传统的单元库不同,它的知识含量更高、规模更大。例如,CPU、运算器、存储器、驱动器、放大器等都可以是IP模块。IC技术发展的过程如图1所示。

IC产业未来的发展

IC产业未来的发展

IC产业未来的发展存在着一些不可阻挡的趋势,大致可概括为以下几点:

(1)摩尔定律仍然有效,直至越来越高的光刻和制造设备成本致使特征尺寸的进一步缩小失去经济上的意义。首先是光罩成本,随着特征尺寸变小,在光刻所包含的数据量急剧增加的同时,光刻成本也呈爆炸性地增长。其次,随着特征尺寸的变化,晶圆制造设备成本将急剧增加。

(2)系统产品中IC所占的比例逐年持续增加,21世纪消费电子产品将成为最重要的IC应用领域。消费电子产品将主导IC的应用,并对IC产业造成巨大影响。因为,对于消费电子产品,更快地实现量产和缩短产品面世时间是获得更多市场份额以及实现较高售价的两个关键因素。为缩短生产及设计时间,就必须要采用新的设计方法、新的设计架构、以及新的EDA设计软件。

(3)由于IC变得更复杂,特征尺寸持续缩小(90甚至65nm),作为IC设计的技术手段,EDA工具对于IC设计产业的成长具有更为关键的作用,巨大的设计挑战继续推动着EDA产业的发展。这些设计挑战主要包括时序收敛、功耗、信号完整性、验证、测试、以及可制造性设计等方面。

(4)IP的使用日益广泛,对SOC的设计来说,设计重用是使IC设计时间缩短的最好方式。到2005 年,SOC中80%以上的电路将使用早已设计好的IP,所以IP对SOC设计是不可或缺的一环。基于平台的SOC设计以可重用的IP为基础。因为有可重用的IP出现,所以许多IC设计厂商就推出一种新的设计方法去缩短设计时间,那就是设计平台。在这个平台之上,已经有设计好的微处理器核、数字信号处理器核、客户的IP、软件和数据总线。也就是说,80%以上的系统功能电路都已经预先设计好了,只要再加上自己的20%的新电路功能,一颗新功能的SOC就出来了。

EDA技术的发展

瓶颈在于设计系统芯片(SOC)正在迅速地进入主流产品的行列。由此引发的“芯片就等于整机”的现象,将对整个电子产业形成重大的冲击。种种迹象表明,整个电子产业正在酝酿着一场深刻的产业重组,这将为许多新兴的企业提供进入这一行业的最佳契机。

目前,半导体供求链最大的瓶颈在于设计高复杂度芯片。针对这一难题,一种行之有效的方案是将芯片设计环节进一步细化,以形成一个新的产业链。行业中被认可的方案是把芯片设计分为两部分,即知识产权IP模块设计和系统芯片集成。通俗一点的说,就是一部分人做“积木”,一部分人搭“积木”。新的供求链更需要新的设计工具和新的开发工具,尤其是横跨软硬件的EDA工具和SOC平台工具。因此,系统芯片设计和实现方法是当前EDA领域研究的热点课题。

EDA技术焦点

目前的EDA产业正处在一场大变革的前夕,对更低成本、更低功耗的无止境追求和越来越短的产品上市压力正迫使IC供应商提供采用0.13μm或以下的千万门级的系统芯片,而这些系统芯片的高复杂性设计更加依赖于EDA供应商提供全新的设计工具和方法以实现模拟前后端、混合信号和数字电路的完全整合。然而,这些新的需求为当代EDA工具和设计方法带来了不少新的挑战与机会,

例如如何在工艺上防止模拟电路与数字电路之间的干扰;现有的大部份EDA工具最多只能处理百万门级设计规模,随着IC设计向千万门级以上规模发展,现有EDA工具和方法必须进行升级。如何融合各EDA供应商的工具,以便向IC设计界提供更高效能和更方便的RTL-to-GDSII或Conc-ept-to-GDSII整合设计环境;为保证深亚微米(0.13μm或以下)和更低内核工作电压(1.8V或以下)时代的信号完整性和设计时序收敛,必须采用新的设计方法。

系统设计步骤从软硬件规格需求开始,包括功能、时序、IO 界面、实体布局面积与耗电功率等重要因素,经过软件硬件模块分割(Block Parti-tioning)成数个模块,而各模块(Block)需要由软硬件设计、验证、合成与整合工程师共同组成。另外,对于SOC的设计必须同时具有处理系统功能、时序、布局等物理设计与验证问题的能力。设计过程中必须有效地使用EDA软件, 如算法仿真(Algorithm)、逻辑合成和仿真系统(Emulation),所以要进一步发展可重复使用的设计数据库,以有效缩短设计时程。目前几项重要EDA技术的发展方向如下。

(1)逻辑虚拟原型技术:由于目前EDA业界将大部份注意力放在解决SOC整合的物理问题上,因此市场上已有很多用以建立硅虚拟原型(Silicon VirtuaLPrototype)的工具。但是,硅虚拟原型并不关心芯片的逻辑架构,它完全可能使一个带有若干逻辑错误的芯片顺利通过物理设计阶段。因此,未来设计流程的重心很可能将转向前端的逻辑虚拟原型。大多数有关虚拟原型的讨论一直集中在建立一个物理虚拟原型,不过,今天ASIC设计的复杂性和高成本要求业界更多地注意逻辑虚拟原型,以确保设计的逻辑是正确的。逻辑虚拟原型是SOC设计的一个关键的新领域,逻辑和架构错误需要在设计师建立RTL代码的设计早期阶段就被识别出来,这可以使设计小组节省好几个星期的时间,并避免昂贵的多次投片。

(2)DFT 工具的发展:RTL设计流程的两个最大挑战是:提高设计师的生产率和确保设计在构造上是正确的,以及包括测试和其它物理实现工具所需的下游设计约束。为了提高设计效率,目前很多公司都在从事设计检查过程的自动化,即使用能做快速合成的软件来预测下游的问题。即使是最有经验的工程师也很难在RTL代码中发现这些问题。

所以各EDA供货商正在积极开发可以检测设计是否具有门级问题的工具。另外,在RTL建立阶段还必须考虑可测试性问题。测试代码对RTL设计师而言通常是不可见的,但要求他们遵守DFT(可测试性设计)规则。测试工程师常常被迫修改门级代码,从而破坏了与RTL代码的链接。再加上不同的测试工具有不同的限制,更进一步加剧了这一问题的影响。因此新的设计方法必须能够在RTL阶段指出可测试性问题。

(3)TBV验证技术:随着几百万门设计和深亚微米工艺的出现,用于功能验证的HDL程序数目会超过100万行,而验证的周期数会成等比级数增加,传统的功能和逻辑验证方法已经不能满足需要, 必须求助于一些新的验证技术, 如TBV(Transaction-baseDVerification) 技术。TBV具有更高的抽象级,这意味着可以花费更少的时间来开发和纠错测试平台,也可以被重复使用,重要的是,容易实现更高的功能覆盖率。

(4)IC实现工具:SOC和复杂ASIC设计的困难度正推动EDA工具向两个明显相反的方向发展:一方面,几百万门设计所导致的巨大数据量迫使工程师采用由上而下的设计方法,这种方法最初阶段采用抽象形式或术语来描述设计;另一方面,随着工艺技术继续向0.13μm以下发展,IC设计工程师必须考虑详细的物理特性对设计时序、功能和可靠性的影响。为了解决这一矛盾,EDA工具必须提供抽象级设计能力(这可使复杂设计的表示非常简洁紧凑),以及必须具备对深亚微米技术的详细物理效应进行测试及验证的能力。现有的物理合成和虚拟原型工具可以在后端处理这一问题,但EDA工具供应商必须继续使IC设计工具链上的所有工具都能综合考虑物理信息,从而在IC设计过程的每一阶段,设计工程师不管做出什么设计修改,都能马上看到实际完成后的效果。

(5)智能型测试平台:随着工艺技术向90nm发展,一系列新的问题逐渐浮上台面。信号完整性、可测性设计、验证和设计重用等正成为前所未有的关键问题。此外,将EDA供应商所有的EDA工具整合成为一个涵盖RTL-to-GDSII的流程,也可以帮助设计师提高设计效率。因此,信号完整性问题必须在一个尽可能高的抽象级得到解决,物理合成和分析工具不仅必须能够分析和发现设计问题,而且应能修复问题。由于智能验证平台提供了一个综合的全自动解决方案,它包含了更高抽象级的基于断言的验证和测试平台技术、更高性能C++建模技术、以及可满足这些需要的先进覆盖率分析技术。综上所述,可知智慧测试能力的重要性,但是独立的时序和功能验证解决方案也非常有价值。由于验证在整个设计周期中占很长的一段时间,因此工程设计小组必须寻求能以最低风险改善生产率和输出的最新解决方案。

(6)开放EDA数据库:开放式API设计数据库也是今后EDA产业成功的一个基本要素。通过它,设计师才能对不同供货商的工具和自己开发的工具的数据进行更高效的处理。由于任何一家EDA公司都不可能提供适合每一个客户需要的所有解决方案,因此开放式EDAAPI标准(如OpenAccess标准)将为IC设计师提供一个各种设计工具都能协同工作的平台。

EDA工具的现状与发展

半导体工艺的每一次跃升都促使EDA工具改变自己,以适应工艺的发展;反过来EDA工具的进步又推动设计技术的发展。可以说EDA工具是IC设计产业的背后推手。

在EDA工具方面,目前全球提供EDA工具解决方案的公司主要有Cadence、Synopsys和Mentor Graphics公司,这三家公司的市场占有率总和超过了60%。为迎接混合信号的发展市场,Mentor Graphics推出AdvanceMS(ADMS)混合验证平台。Cadence和Synopsys公司也有相应举动。值得一提的还有MagmA公司,Magma的Blast Fusion 是完整的从门级网表到芯片的物理设计系统,它包括物理综合和优化、布局布线、时钟树生成、平面布局和功耗规划、详细布局布线、RC的提取和内嵌增量时序分析工具。它利用FixTiming方法有效地消除设计返工迭代时间,在逻辑设计和物理设计之间无需迭代,统一数据库模型又能做到物理实现和分析各模块并行工作,以确保设计正确。

来源:电子设计应用 作者:袁丽晖 时间:2006/10/31 0:00:00