# 先进混合讯号微控制器的除错策略

By Keith Coffey, Silicon Laboratories Inc.

在过去 30 年里,微控制器已演变成为跨越众多领域的 100 亿美元全球市场,尽管这个市场已经非常成熟,厂商仍继续以 8 位处理器为基础,发展各种创新的解决方案。8 位的 8051 架构是在 1980 年代首次推出,此后它就吸引了庞大而忠实的用户群。这些年来,不断的技术创新使它拥有更多的功能特色,例如现场可烧录的程序内存、整合式模拟数字转换器和加强型串行通讯功能;藉由提高效能、整合度和弹性,新型 8051 微控制器系列正将新的生命力注入现有架构,这些组件也已真正成为系统单芯片 (SoC) 产品。

这些组件采用先进的整合技术,迫使嵌入式软件开发和除错程序必须面对许多新的挑战。原始程序层级的软件开发和除错工具对于复杂系统固然重要,嵌入式系统除错的关键却在于原始程序显示窗口和硬件之间的连结。虽然传统的嵌入式系统发展技术一直都很适合只有很少或完全没有模拟功能的低产出控制器,但这些方法却不足以应付最新的系统单芯片产品。

在 8 位的世界里,嵌入式系统研发人员通常会依赖三项基本的除错策略,分别是EPROM/OTP 原型、目标监督程序或线内仿真器 (ICE) 系统,但是对于先进的混合讯号微控制器,拥有最大优势的却是芯片内建除错系统。以下我们将逐一分析这些方法,还有它们是否适合复杂的新型嵌入式系统。

#### EPROM/OTP 原型

传统上,嵌入式系统的最基本发展方法是 EPROM/OTP 原型。在这种方法中,研发人员先在桌上型计算机利用汇编语言或 C 语言设计软件,然后将编译所得的目的码烧录到 EPROM、OTP 或是 EEPROM 组件,再将目标组件安装到原型电路板预留的组件插座以进行除错。研发人员接着会测试系统以决定其功能是否正常,发现错误后,他们会修改原始程序,烧录新组件,把新组件安装至插座,然后重复整个测试程序。

过去,这种软件开发方法的成本都很低,效果也很好,但是对于先进的混合讯号组件,这种做法很快就变得没有生产力。随着功能整合度不断提高,厂商开始把更多的程序内存、数据存储器和处理器效能加入控制器,使它能够执行更复杂的软件程序。然而对于系统内部的工作情形,这颗原型芯片却只能提供很少或完全无法提供任何的能见度(visibility),研发人员必须加入软件 hook (例如切换外部接脚) 来监视

程序的执行和目标装置的行为,这种做法使得程序的设计、烧录和测试过程变得非常冗长,很快就让人觉得疲倦厌烦。

芯片封装是这类发展工具的另一项困难。随着终端系统日益复杂,研发人员被迫在更小的封装内挤进更多的电路,不同的系统空间需求也可能让组件插座变得不切实际。为了克服系统空间的限制,芯片厂商开始提供高接脚数的表面粘着封装,但这些组件却很难以人工方式安装至电路板或进行重焊,这使得 EPROM 原型法在实际上并不可行。

# 监督程序 (Monitor Code)

为了解决 EPROM/OTP 原型法的能见度缺点,设计人员所采取的下一步通常是把软件监督程序加入目标组件,这个目标监督程序会透过串行联机与个人计算机上的除错程序通讯,进而为目标组件提供基本的线上执行控制 (in-system run control),例如执行 / 停止、单步执行和软件断点;断点会在目标组件的程序内存中以跳跃指令取代原有指令,由这个跳跃指令把控制权转交给监督程序。

整体来说,这种方法会提供更强大的除错能力,因为研发人员可于终端系统工作时查询目标组件的状态;但另一方面,这种方法却须占用目标系统的使用者资源来提供串行联机和命令界面。除此之外,储存于 ROM 内存的程序代码也无法以这种方法进行除错,因为监督程序必须修改程序内存以取得执行控制。由于监督程序通常是目标系统上的中断驱动型软件程序,所以使用者并无法在中断服务例程内设定断点;在复杂的嵌入式系统中,中断例程可能是整个程序的重要部份,因此无法在中断例程内除错就成为很严重的缺点。

#### ICE 系统

ICE 仿真器是最高阶的 8 位发展系统,它包含仿真器转接盒 (emulator pod),其中的电路可以准确再生目标装置的行为,这个转接盒会透过末端附有插座的缆线来取代目标系统的控制器。

ICE 系统的主要优势是它提供目标装置内部工作情形的完整能见度,研发人员可以准确看到程序执行时所做的事。基本的 ICE 系统会提供仿真所需的 RAM 内存来储存目标程序,它还会提供复杂的断点功能,多数的 ICE 系统还包含实时追踪功能,每个时脉周期可读取数百次或数千次的接脚状态及内部变量,这项功能对于复杂实时问题的除错特别有用。就软件的观点而言,ICE 系统属于非侵入性,因为仿真器的动作与真正的目标组件完全相同。

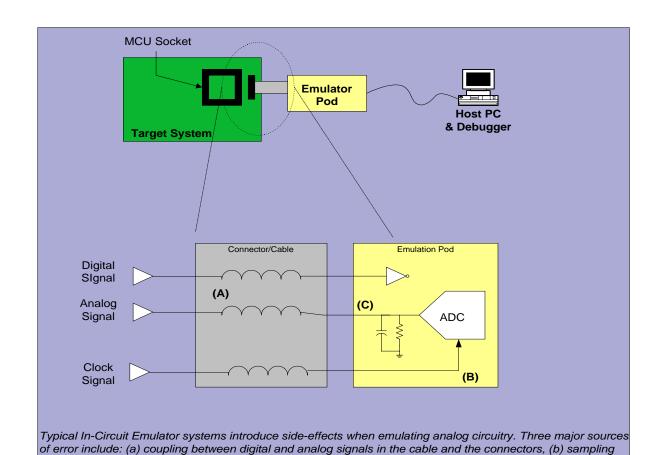

当然,所有这些功能都必须付出代价。全功能 ICE 系统的价格可能高达 25,000 美元 – 就算 8 位系统也是如此。另外,随着时脉速度增加,要设定系统让 ICE 发挥作用也变得更困难,因为缆线和装置内的联机都会造成额外的讯号延迟,尤其是先进的模拟系统,仿真器的缆线更是重要考量之一。缆线电感、寄生耦合和干扰若凑在一起,将会让模拟电路的精确仿真变成不可能 (图 1),因此混合讯号系统的研发人员只能将 ICE 用于数字行为的除错,他们必须等到设计流程后期,才能决定真正的模拟效能。

图 1:将 ICE 用于混合讯号控制器的副作用

error or jitter due to additonal delay in clock signals, and (c) the combination of cable inductance and parasitic input impedance in the emulation prototype system. All these error sources alter the behavior of the prototype

### 更好的解决方案:芯片内建除错功能

system and could mask potential problems with the production hardware.

理想情形下,嵌入式发展和除错系统应提供简单的程序烧录方法、目标系统的内部能见度以及实时控制 — 而且这些功能的成本必须合理,结合可线上烧录 (in-system

programmable) 的闪存以及少量的芯片内建专属除错逻辑,就能提供这样的发展环境。

要提供有效的芯片內建除错系统,第一个要素是利用可线上烧录的闪存担任程序内存。无论研发前或研发后,线上烧录都有许多优点;简单快速的烧录功能会加快发展速度,因为程序的修改变得轻松快速,硬件也不必改变,这能减少所需的发展时间和降低成本。另外,内建闪存的组件还能减少设计风险,因为研发人员可于流程后期修改软件,它还能支持远距或客户现场的软件升级,使得维护成本变得更低。

把线上烧录和整合式逻辑结合在一起以支持除错应用,就能够创造出一套强大而低成本的发展系统。芯片内建除错系统还包含专用的串行联机,它可以和个人计算机的软件进行通讯,为目标组件提供除错和烧录界面。这种软硬件组合带来一套完整的嵌入式软件开发环境。

芯片内建除错方法的优点有许多,例如它不会占用系统的任何使用者资源,因为烧录器/除错器都有自己的专属界面,芯片内建的除错逻辑则会利用硬件提供实时执行控制。这种技术属于非侵入性,因为使用者的程序代码无需修改,就能在目标系统上进行实时除错。这种除错环境的成本也低于 ICE 系统。

芯片內建除错功能对于精准模拟系统特别有用,例如在研发过程中使用正式生产的 组件就是一项重要优点,因为研发人员可以评估整个系统效能,包含基板布局和寄 生参数效应。由于不需要仿真器转接盒,所以也没有额外的缆线、插座或探针来干 扰模拟效能,这能带来真正的模拟子系统实时除错能力。

这类芯片内建除错系统在 32 位微控制器领域已司空见惯,但大多数的 8 位架构尚未采用这些技术,然而对于更先进的混合讯号系统单芯片,内建于芯片的除错能力就极为重要。

| 除错方法     | 线上烧录 | 目标能见度 | 执行控制 | 模拟副作用 | 成本 |

|----------|------|-------|------|-------|----|

| EPROM 原型 | 没有   | 低     | 无    | 低     | 低  |

| 目标监督程序   | 没有   | 中     | 中等   | 低     | 低  |

| ICE      | 有    | 非常高   | 完整   | 高     | 高  |

| 芯片内建除错   | 有    | 高     | 完整   | 低     | 低  |

表 1:除错方法的比较

## Silicon Laboratories 的 C8051 系列

Silicon Laboratories 的 C8051F 产品是以 8051 指令集架构为基础,但采用全新的专属实作方式,效能超过原始 8051 组件 20 至 25 倍。C8051F 组件结合 8051 兼容处理器核心、高精准度的模拟外围以及可线上烧录的闪存,进而带来种类丰富的先进系统单芯片解决方案。该公司最新的 C8051F064 产品系列提供 25 MIPS 的 8051 处理器、两组 1 MSPS 的 16 位逐次渐近式 (successive approximation) 模拟数字转换器以及最高 64 kB 的可线上烧录闪存。

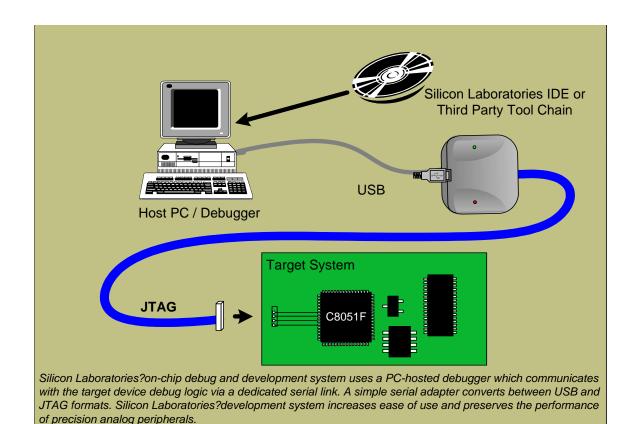

所有 Silicon Laboratories 微控制器都拥有完整的发展套件,它能提供 ICE 仿真器的常用功能。C8051F 芯片内建除错逻辑使用 JTAG 为基础的专属串行除错界面,最多同时支持 4 个硬件断点。利用在个人计算机上执行的除错程序,使用者可以查看和修改内存位置、设定和清除断点、单步执行和修改闪存内容。 Silicon Laboratories 的整合发展环境 (IDE) 软件提供原始程序层级的汇编语言或 C 语言除错功能,它还能将其它厂商的编译器整合至此环境中。所有的除错和发展都是在使用者目标硬件上利用正式生产的组件进行,完全不需要仿真器硬件。除错逻辑确保在进行除错时 (例如单步执行),外围装置与原始程序窗口会亦步亦趋的执行相同指令 (lock-stepped),另外它还能支持中断服务例程的除错 (图 2)。

图 2: 芯片内建除错系统的范例

Silicon Laboratories 的芯片內建除错系统能实现先进混合讯号控制器发展系统的主要目标:简单的烧录界面、绝佳的目标系统能见度、实时控制和低成本,而且不会对模拟效能造成负面影响。

#### 下一步是什么?

目前内建除错 / 发展支持功能的先进混合讯号控制器都能在产品好处和成本之间提供绝佳的取舍选择,但我们应能合理假设这些芯片内建除错系统的功能会随着时间加强。藉由 32 位控制器的带领,这些芯片内建除错系统的部份更先进功能很快就会扩散到 8 位世界;在理想情形下,一套强大可靠的发展系统将提供 ICE 仿真器的大部份功能,成本却只有它的几分之一。对于 8 位系统来说,目前的芯片内建除错硬件所缺少的一项重要功能就是实时追踪,研发人员应寻找可于未来提供更强大追踪能力的厂商,实时程序追踪功能就是这项要求的很好起点。或许在短期之内,它们就会提供更多的硬件断点、复合断点 (complex breakpoint) 以及条件资料断点。

厂商已开始提供产出更高的核心,这让更丰富的模拟功能、更大的芯片内建内存和更多的除错支持变得极为重要。系统研发人员必须面对更复杂的系统、更紧迫的发展时程和更少的预算,他们需要控制器厂商提供使用简单、低成本而容易除错的系统。