# **USB Audio 2.0 Solution**

-----Based XS1-L8A-64-LQ64

本文描述了设计一个基于 XMOS XS1-L8A-64 的 DSD 音频的方案。

#### 1、XMOS 供电

XMOS 需要 VDDIO、VDD 和 PLL\_AVDD 三个电源输入。

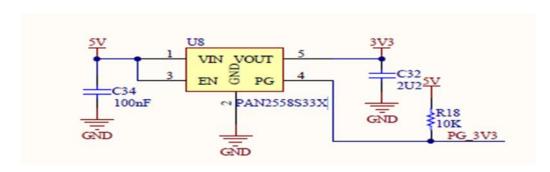

1) VDDIO 是 I/O 电压, XMOS 采用 3.3V 的 IO 电压, 如下:

图 1

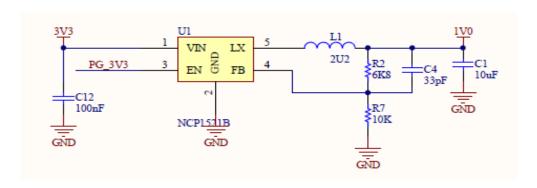

2) VDD 是 XMOS 芯片所需的 1.0V 内核电压,如下:

图 2

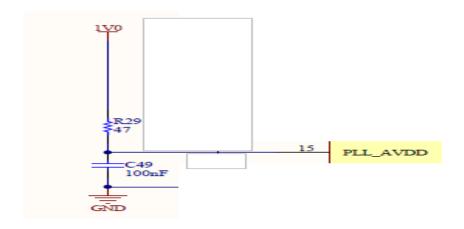

- 3) PLL\_AVDD 为 1.0V 的 PLL 锁相环电压,与 VDD 共用一路 1.0V 电源。

- 4) 附加电路需求

47 欧姆的电阻和 100nF 的瓷片电容,构成 PLL\_AVDD 的一阶无源低通滤波器。

图 4

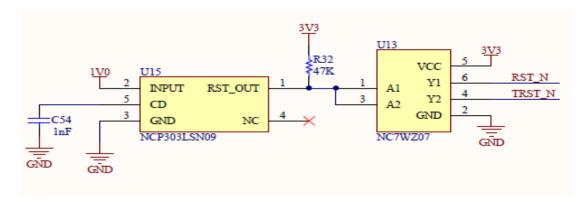

#### 2、Power On Reset

RST\_N 和 TRST\_N 脚在上电后,拉低是有效的。

RST\_N 是一个全局异步复位,低电平有效,低电平时间至少为 100 ns。TRST\_N 为 XTAG 的复位,与 RST\_N 类似。

系统采用电压监测复位的方式,NCP303LSN09 为电压监测芯片。NC7WZ07 为双缓冲芯片,连接到 RST\_N 和 TRST\_N 脚,在电压监测复位和系统复位直接起到缓冲作用。当 RST\_N 拉低的时候,处理器保持复位状态,复位期间所有 GPIO 呈是高阻态,释放 RST\_N 之后,处理器开始内部复位。具体电路下图所示:

#### 3, Clock

在 15—150us 的时间(依赖内部时钟),所有的 GPIO 都有内部拉阻使能,处理器是基于时钟速度,这个时钟的速度是靠 mode1 和 mode2 的设置。

处理器的时钟速度取决于 MODEO 和 MODE1, 如下图所示:

| Oscillator | MODE |   | Tile           | PLL Ratio | PLL settings |     |   |

|------------|------|---|----------------|-----------|--------------|-----|---|

| Frequency  | 1    | 0 | Frequency      |           | OD           | F   | R |

| 5-13 MHz   | 0    | 0 | 130-399.75 MHz | 30.75     | 1            | 122 | 0 |

| 13-20 MHz  | 1    | 1 | 260-400.00 MHz | 20        | 2            | 119 | 0 |

| 20-48 MHz  | 1    | 0 | 167-400.00 MHz | 8.33      | 2            | 49  | 0 |

| 48-100 MHz | 0    | 1 | 196-400.00 MHz | 4         | 2            | 23  | 0 |

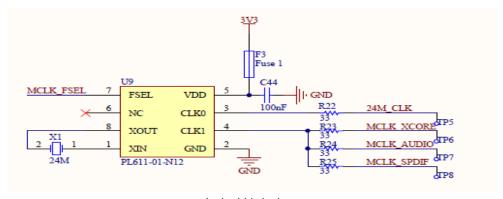

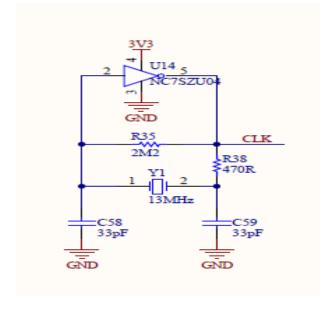

PL611-01 为多路时钟芯片,第七脚为功能复用引脚,在本电路中作为时钟选择引脚,该引脚可以选择 CLK1 的输出时钟为输入时钟或者输入时钟的二分频,CLK1 外部器件提供时钟;CLKO 输出时钟等于输入时钟。由于 MODEO 和 MODE1 已设置 XMOS 工作时钟为 13MHZ,所有采用下面的 13MHZ 时钟电路,并给 USB 提供时钟。MCLK\_AUDIO为 ADC 和 DAC 提供时钟,MCLK\_SPDIF 为 SPDIF 提供时钟,MCLK\_XCORE是为 ADC 和 DAC 提供 DSD\_CLK 和 LRCLK 而引入的外部输入时钟,MCLK\_XCORE经由处理器处理后作为 ADC 和 DAC 的 DSD\_CLK 和 LRCLK时钟。

多路时钟电路

XMOS 13MHZ 内核频率

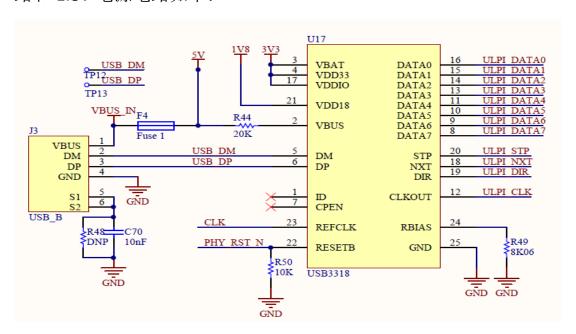

#### 4, XMOS USB Interface

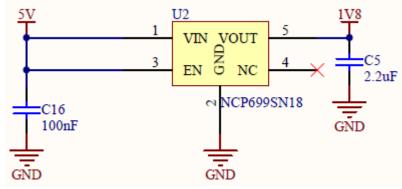

XnD12--- XnD23 作为 ULPI 接口, 当有 USB 接口的时候, XnD02-- XnD09, XnD26--- XnD33, XnD37-- XnD43 以及 XnD12--- XnD23 的 ULPI 接口不能作为其他功能 IO 使用。USB3318 需要 1.8V 和 3.3V 的工作电源以及一个 3.3V 的 IO 电压, 1.8V 电压由 NCP699SN18 提供。USB 电路和 1.8V 电源电路如下:

## 5, ADC 和 DAC 电路

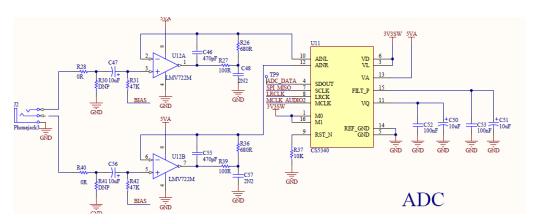

1. ADC 选用的是 CS5340,同时支持 DSD 和 PCM 两种方式。ADC 接口采用从模式时钟输入,此时 M0 和 M1 都要求拉高;MCLK 为 delta-sigma module 提供时钟;SDOUT 码流输出连接到 XMOS 的 ADC\_DATA 输入端(X0D24);SCLK 是数据时钟端,LRCLK 是左右声道时钟端,当从模式时钟输入时,则 SCLK 和 LRCLK 由 XMOS 提供时钟给这两个端口;AINL,AINR 是左右声道模拟输入,由双运放 LMV722M 作为模拟信号的前级放大,电路如下图所示。

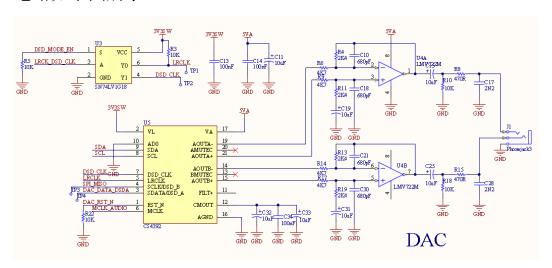

2. DAC 选用的是 CS4392,同时支持 DSD 和 PCM 两种方式。通过 M0、M1 和 M2 来定义码流格式及格式选择; MCLK 为 delta-sigma module 提供时钟; SCLK/DSD\_B 和 SDATA/DSD\_A 为 DSD 和 PCM 两种 模式的复用引脚,连接到 XMOS 的 DAC\_data 数据输出端(X0D11)和

SPI\_MISO 数据输出端(X0D0),LMV722M 为模拟信号的输出放大; 电路如下图所示:

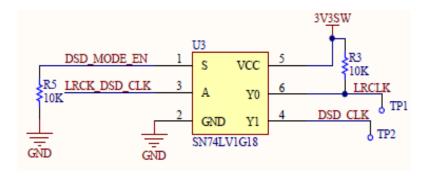

3 .X0D10 和 DSD\_MODE\_EN 作为 SN74LV1G18 的控制产生 SCLK 和 LRCLK 时钟, 电路如下:

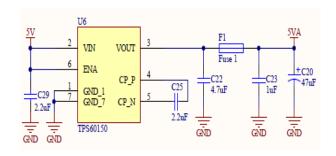

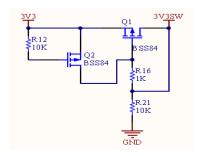

4.ADC 和 DAC 的电源作为模拟电,要与 XMOS 部分的电源隔离分开使用,5V 的模拟电源由 TPS60150 提供,3V3 的模拟电源由 MOS 管隔离放大提供,如下图所示:

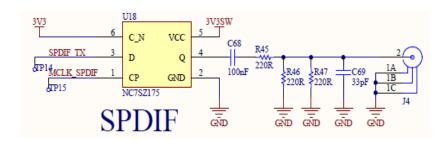

### 5.NC7SZ175 为 SPDIF 提供逻辑转换:

#### 6、boot

当系统选择为SPI Flash 启动时,SPI Flash 的四个引脚连接到 x0d0, x0d01, x0d10, 和 x0d11。若不是 SPI Flash 启动,则通过 OTP 或 JTAG 来启动。MODE[3:2]两个脚控制设备启动方式。

| MODE[3] | MODE[2] | Boot Source                              | 1 |  |

|---------|---------|------------------------------------------|---|--|

| 0       | 0       | None: Device waits to be booted via JTAG | 7 |  |

| 0       | 1       | Reserved                                 | ŀ |  |

| 1       | 0       | xConnect Link B                          |   |  |

| 1       | 1       | SPI                                      |   |  |

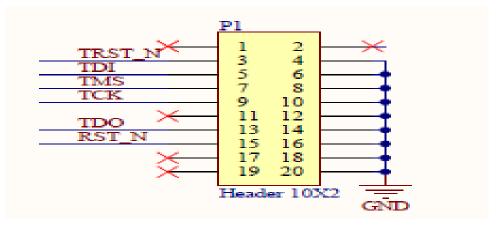

#### 7. JTAG, XScope, and debugging

开发一套 XMOS 产品需要 XMOS 工具和 XTAG 调试器,需要一个 XSYS 接口。XMOS 有三种类型的 XSYS 接口:G.1 No xSYS header,G.2 JTAG-only xSYS header,G.2 Full xSYS header。

- 1.如果你不用 xSYS 头,你必须提供自己的方法来烧写 OTP/flash 和调试。

- 2.xSYS 头连接到 xTAG 调试器,如果 MODE2 配置为高电平,连接 mode2 到 xSYS 头的 3 脚,但不要连接到 VDDIO。如果 MODE3 配置为高电平,连接 mode3 到 xSYS 头的 3 脚,但不要连接到 VDDIO。如图 18 图 18

3.Full xSYS header,连接方式与 JTAG-only xSYS header 相似,有几个端口要改动。连接 2-wire xCONNECT Link 到 the xSYS header.如下; xlb1out(x0d16)引脚连接到 XSYS 头的 6 脚,还要一个 33r 串联电阻接近该装置。xlb1out(x0d17)引脚连接到 XSYS 头的 10 脚,还要一个 33r 串联电阻接近该装置。XLB0in (X0D18)连接到 xSYS header 的 14 脚.XLB0in (X0D19)连接到 xSYS header 的 18 脚.

## 9, Multi device designs

- 1.一个设备连接到一个 SPI Flash 引导。

- 2.从 link 启动的设备必须 mode2 接地, mode3 不接, nc 状态。

# Xmos 特许一级代理商

### 茂晶有限公司

# 國內服務據點:

深圳: Tel: 86-755-8828 5788-1207 Email: <u>Shenzhen@gfei.com.hk</u>

北京: Tel: 86-10-5126 6624 Email: Beijing@gfei.com.hk

上海: Tel: 86-21-54453155 Email: Shanghai@gfei.com.hk

武漢: Tel: 86-27-8730 6822, 8784 0783 Email: Wuhan@gfei.com.hk

青島: Tel: 86-532-8573 1420 Email: <u>Qingdao@gfei.com.hk</u>

成都: Tel: 86-028-85548390 Email: Chengdu@gfei.com.hk

廈門: Tel: 86-0592-5302668 Email: Xiamen@gfei.com.hk

### 海外服務據點:

香港: Tel: 852-3741 0662-2293 Email: <u>Hongkong@gfei.com.hk</u>

台灣: Tel: 886-2-89132200 Email: Service@gfei.com.hk

# 技術支援:

深圳: Tel: 86-755-8828 5788-1207 Email: royl@gfei.com.hk

上海: Tel: 86-21-54453155 Email:

北京: Tel: 86-10-5126 6624 Email: jackl@gfei.com.hk