基于ADSP-TS101高速信号处理系统采用了集成系统设计,硬件部分引入信号完整性分析的设计方法进行高速数字电路的设计,要解决系统中主处理器在较高工作频率300 MHz下稳定工作的问题,以及在两个主芯片之间和主芯片与数据存储芯片之间数据高速互联的问题,提高系统的性能,满足设计要求。

1 系统硬件设计

1.1 数模混合部分的设计

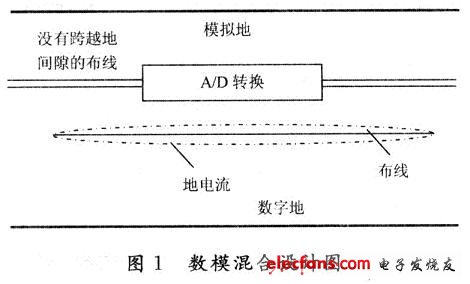

A/D是数字和模拟混合部分,是设计重点考虑的部分之一。数字部分的频率高,模拟部分对于扰很敏感,处理不好,数字信号很容易干扰模拟信号,出现电磁干扰问题。降低数字信号和模拟信号间的相互干扰,要掌握电磁兼容的两个原则:尽可能减小电流环路的面积;系统只采用一个参考面。

系统仅有一个A/D转换器,采用混合信号PCB的分区设计,即使用同一地,如图1所示。将PCB分区为模拟部分和数字部分,在A/D器件的下面把模拟地和数字地部分连接在一起。保证两个地之间的连接桥宽度与IC等宽,所有信号线一般都不能跨越分割间隙,跨越分割间隙的信号线要位于紧邻大面积地的布线层上。电路板的所有层中数字信号只能在电路板的数字部分布线,模拟信号只能在电路板的模拟部分布线,模拟和数字电源分开。

1.2 高密度(HD)电路的设计

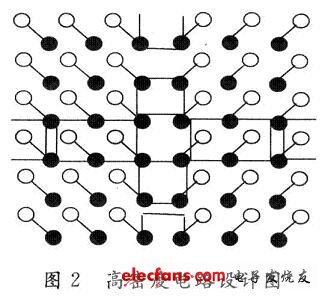

TS101硬件电路的设计属于高密度电路,是整个印制板设计的难点之一。TS101采用BGA封装,焊球25×25阵列,焊球之间间距为1 mm,没有空白区。焊盘直径的下限是O.45 mm(18 mil),这里采用0.51 mm(20 mil)。1每个焊盘都是表贴(无通孔)无阻焊。对最外圈的两排焊球,信号线直接从表面层直接引出,内圈焊球向外的引线采用打过孔的方式,从焊盘向对角引线,在4个相邻焊盘的对角线中间打一个外径O.5 mm(20 mil),内孔径O.25 mm(10 mil)的带阻焊通孔,然后将信号线从电路板的其他层引出去。这些引线的线宽和线距的下限都是0.15 mm(6 mil)。

TS101一般工作在250 MHz或300 MHz,为保持电源和地层的连续性和较好的去耦效果,设计中采用AD公司推荐的连接方式,用6个0.1μF和2个0.01μF的贴片电容焊在与TS101芯片中央位置相对的电路板的另一面,其连接方法如图2所示。图中方块部分为去耦电容。

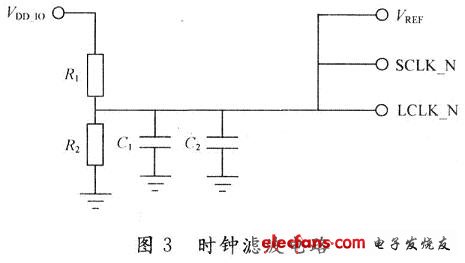

1.3 系统时钟设计

TS10l内核时钟最高可以是输入时钟的6倍。内核时钟最高只能工作在250/300 MHz,系统时钟SCLK输入范围为40~100 MHz。为确保时钟的稳定性,增加专门的滤波电路,如图3所示。其中,R1△2 kΩ,R2△1.67 kΩ,C1△1μF(SMD),C2△1 000 pF(HF SMD),并应贴近DSP引脚放置。该电路同时为参考电压输出、系统时钟和局部参考时钟提供了参考电压,电压值为1.5 V±100 mV。

PCB设计时为保证时钟的稳定性采取了以下措施:

(1)用一个晶振作为多处理器系统的同频同相时钟。

(2)同一电路板上各个DSP的时钟用同一个驱动器的各个门分别并行驱动。

(3)在印制板布局时将时钟部分放于印制板中央位置,使时钟驱动线到各DSP的距离大体相等。四是在印制板布线时,时钟线尽可能地靠近地线层。

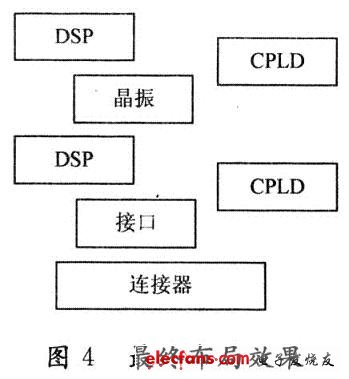

1.4 布局

PCB尺寸过大时,印制线条长,阻抗增加,抗噪声能力下降,成本也增加;过小,则散热不好,且邻近线条易受干扰。确定PCB尺寸后,再确定特殊元件的位置。最后,根据电路的功能单元,对电路的全部元器件进行布局。结合EMC设计一般布局规则,最终布局效果如图4所示。

1.5 布线

根据PCB布线的原则完成布线设计后,需认真检查布线设计是否符合设计者所制定的规则(DRC检查),同时也需确认所制定的规则是否符合印制板生产工艺的需求:

(1)线与线,线与元件焊盘,线与贯通孔,元件焊盘与贯通孔,贯通孔与贯通孔之间的距离是否合理,是否满足生产要求。

(2)电源线和地线的宽度是否合适,电源与地线之间是否紧耦合,在PCB中是否还有能让地线加宽的地方。

(3)对于关键的信号线是否采取了最佳措施,如长度最短,加保护线,输入线及输出线被明显地分开。

(4)模拟电路和数字电路部分,是否有各自独立的地线。

(5)后加在PCB中的图形(如图标、注标)是否会造成信号短路。

(6)对一些不理想的线形进行修改。

(7)在PCB上是否加有工艺线,阻焊是否符合生产工艺的要求,阻焊尺寸是否合适,字符标志是否压在器件焊盘上,以免影响电装质量。

(8)多层板中的电源地层的外框边缘是否缩小,如电源地层的铜箔露出板外容易造成短路。

2 仿真结果

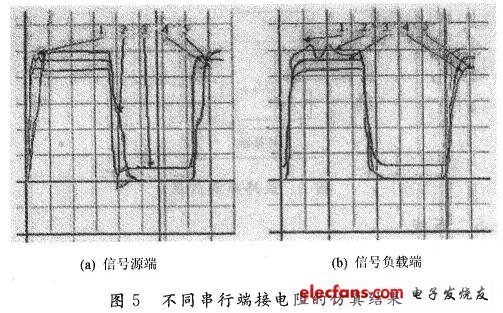

2.1 不同串行端接电阻的仿真

图5为使用不同的端接方式后的信号源端与负载端的波形,图5(a)为信号源端的波形,图5(b)为信号负载端的波形。图5中,1为未加端接前信号源端与负载端的波形;2为使用串行端接方式(端接电阻50 Ω)后的信号波形;3为使用戴维宁端接方式(上拉电阻100 Ω,下拉电阻100 Ω)后的信号波形;4为使用简单并行端接方式(下拉电阻50 Ω)后的信号波形;5为使用RC并行端接方式(下拉电阻50 Ω,电容0.1μF)后的信号波形。

由图5可见,几种阻抗匹配的端接方式都能不同程度地抑制了信号的反射,说明在存在较大反射的电路中使用合适的端接方式能够收到很好的效果。

2.2 链路口仿真

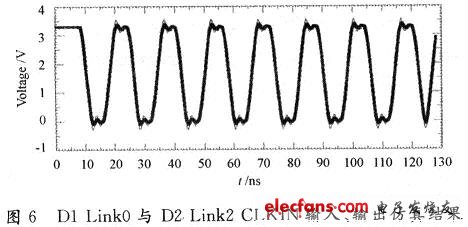

第一组:TS101 D1 Link0和TS101 D2 Link2连接LCLKIN信号,该信号印制线较长且速度要求较高(LAY 7层)。

测试条件:输入同步脉冲序列1010-1010-1010-1010,频率125 MHz,抖动10 ps,该序列为模仿CLKIN时钟信号得到的信号波形,如图6所示。

图6中加粗部分为输入,细线为输出。由图可知,信号基本保持了完整性,上升沿和下降沿的单调性未发生改变。虽然仿真频率高达125 MHz,但是波形的完整性保持完好。

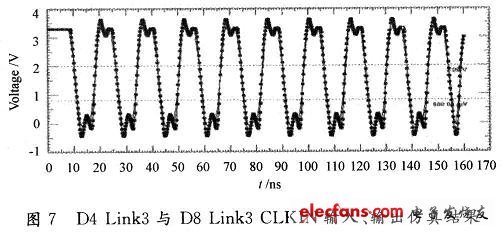

第二组抽取Lay 6层的Link走线最长的一组进行分析,以D4 Link3和D8 Link3的连接为例。思路同上,仿真波形如图7所示。

情况比Lay 7层稍差,但过冲在420 mV左右,满足条件。

3 结 语

随着高速数字电路的发展,PCB密度、速度的提高,以及工艺方面的限制,信号完整性及电磁兼容问题会越来越突出,但只要依据一定的设计准则,通过仿真软件,可以把高速设计中的问题解决好。