引言

税控设备是国家税务部门实施税收管理信息化的必然手段之一,税控器作为税控设备之一,它是在计算机等电子设备的配合下实现税控功能的电子装置,能保证数据的正确生成、可靠存储和安全传输,同时能满足税务机关的管理和数据核查等要求。它内部装有自动记录,但不能更改和抹掉计税存储器,由于系统记录着每日的营业数据和应纳税额,因此可作为向税务机关纳税的凭据。这就决定了税控器中必然要包含可靠的存储芯片。事实上,在众多型号的存储芯片中,AT45DBl6l芯片则更加适合在税控器中的应用。

税控器的总体概述

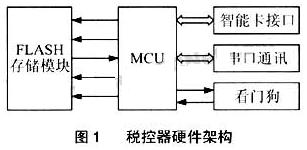

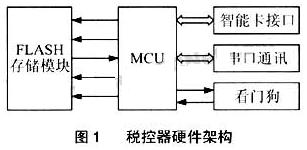

税控器的总体概述税控器平台应具有实时时钟和记录税控数据的大容量存储器、符合ISO 7816标准的IC卡读写器,以及支持税控卡、用户卡和税务管理卡。要能通过USB或串口与主机通信,同时要具有在掉电后可保存存储器数据和时钟运行的备份电池。其内部硬件系统结构见图1所示。

FLASH存储芯片

FLASH存储芯片AT45DBl61是Atmel公司推出的大容量串行Flash存储器,采用串行外围接口SPI系统;同时具有体积小、容量大、功耗低和硬件接口简单等特点,非常易于构成微型低功耗的测量系统。最大时钟频率可达到20MHz,它支持页和块(1块=8页)擦除功能。存储器有4 096页,每页528B容量,并有两个528B的缓冲区,共2MB存储空间。

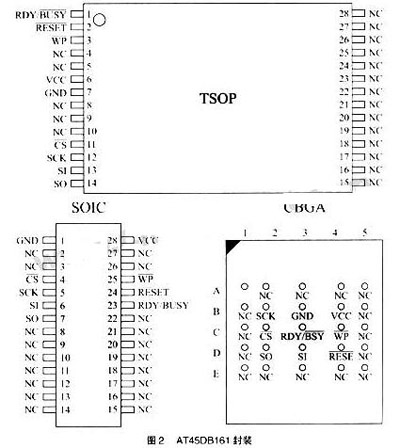

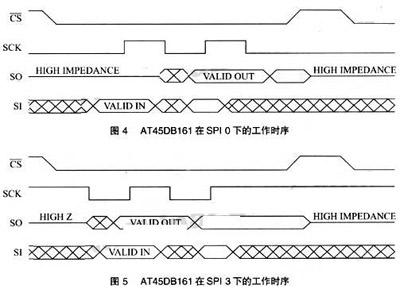

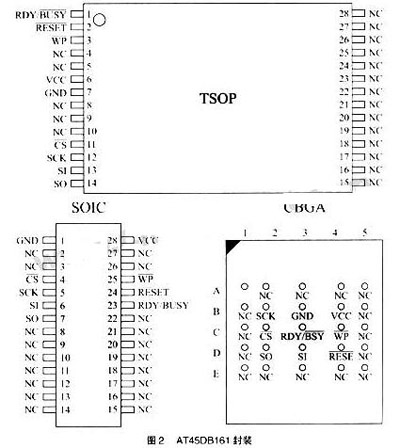

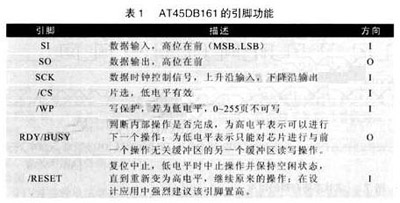

◇AT45DBl61的引脚功能 AT45DBl61具有28脚TSOP、28脚SOIC和24针CBGA等封装形式。图2所示是其引脚排列。各引脚的主要功能如表1所列。

◇操作模式

AT45DBl61的操作码有26条,按操作对象的不同可以分为与页相关操作和与页无关操作;与页相关操作包括:读主存页、主存页数据拷贝到缓冲区、主存页与缓冲区数据比较、缓冲区数据写入主存页、页擦除、块擦除、页编程和页重写等;与页无关操作则包括:读缓冲区、写缓冲区和读状态寄存器。其中缓冲区数据写入主存页的操作中又包括写前擦除和边写边擦,具体应用要依据实际情况来定:如果写数据前已确保该页被擦除(数据全是0xFF),则可使用写前擦除操作来减少操作时间,以提高系统的速度;而如果不能保证该页已经被擦除,为保险起见,建议使用边写边擦操作来提高系统的可靠性。

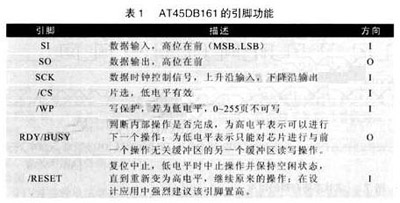

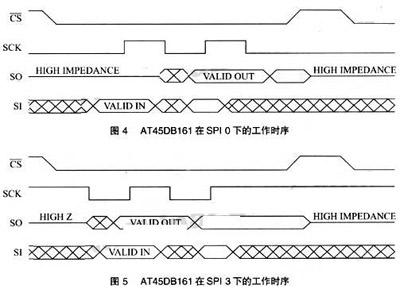

AT45DBl61支持SPI系统工作方式,SPI的四种工作方式如图3所示。

其中支持SPI 0和SPI 3两种方式的时序图分别如图4和图5所示。

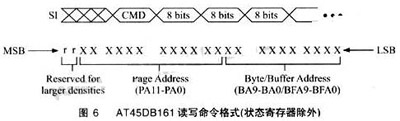

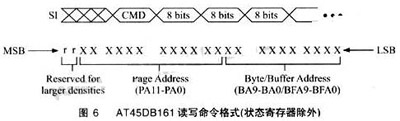

对于不同的操作模式,即使在执行相同的操作时,其操作码也可能不同。如读存储页操作,SPI 0模式下的命令代码为52H,而SPI 3模式下的命令代码则为D2H。除读状态寄存器外,所有的命令格均示于图6图中的rr:代表保留位,建议清零。

操作时,MCU首先向AT45DBl6l发送1个命令字节,其后跟随24位地址数据(前两位为保留位,其后12位为页地址选择位,最后10位为页内开始字节地址),最后根据不同的操作对SI执行不同的处理。如写操作后面紧跟着待写入的数据(高位在前),那么,读存储页就要延迟32个SCK时钟周期以处理读操作,读缓冲区则需延迟8个SCK时钟周期。读状态寄存器的时序(SPI 0)如图7所示。

读状态寄存器(SCK上升沿写入)时,在写入命令字节(57H)后,如没有地址数据,那么,在其后的8个SCK周期就可以直接从SO读取STATUS数据,而且可以连续读取,直到片选信号/CS置高为止。

&nbs

p;

基于AT45DBl61税控器的存储电路设计

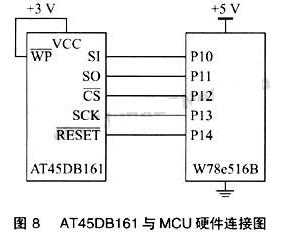

◇系统硬件设计

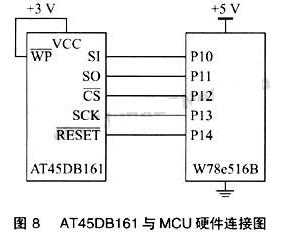

图8所示为AT45DB16l与W78E516B连接示意图。虽然FLASH的工作电压和MCU不同,但它们都不需要电平转换,两者仍能正常通讯,从而简化了电路设计,节约了系统成本。由于WP接高电平,因而去掉了FLASH前256个字节的写保护功能,并且不会对系统的安全造成隐患,同时还节约了单片机的I/O口资源。为了保证对FLASH操作的可靠性,上电后,可对FLASH在操作前复位一次。AT45DB16l的RDY没有占用单片机的I/O口,可在软件处理中通过读状态寄存器的方法来确定FLASH内部操作是否处于忙状态。

◇系统软件设计

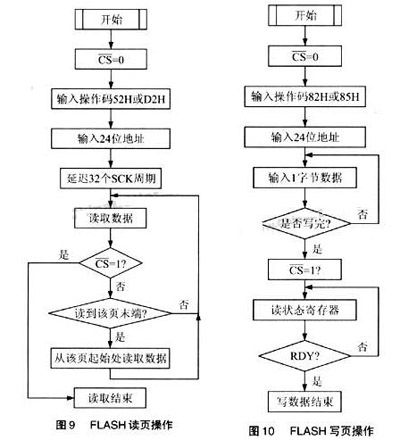

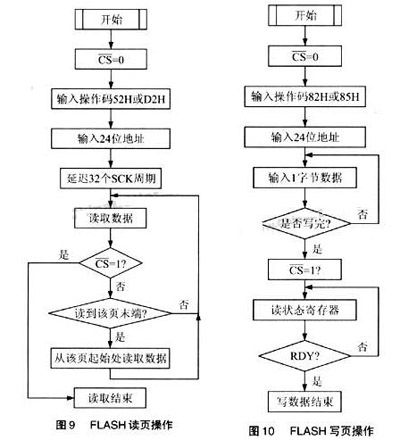

系统中包含智能卡的读写、FLASH读写和串口通讯处理操作,对于智能卡读写和串口通讯处理,由于和本文的侧重点相关不大,就不再一一介绍了。FLASH的读写操作主要包括读缓冲区、读存储页、读状态寄存器、写缓冲区和写存储页。下面以FLASH的读写存储页的操作为例,简要介绍一下软件处理流程。

FLASH写数据过程都采用先写入缓冲区,再从缓冲区写入存储页中方法,且数据都是以页为单位,每次要写入528个字节。如果只修改页中部分数据,而保留该页其他数据,那么,必须先把该页数据拷贝到缓冲区中,然后调用写缓冲区操作,再把缓冲区的数据写入该存储页中。

结束语

AT45DBl61串行FLASH存储芯片在税控器中的实际应用效果很好,而且编程也比较简单,与其它一些FLASH存储芯片相比,AT45DB16的突出特点是电路简单,存储容量大,占用系统资源少。

来源:中电网 作者:杭州电子科技大学 邹杰 时间:2006/9/18 0:00:00