在嵌入式系统处理器中有相当一部分处理器不带SPI接口,但基丁SPI接口的设备非常丰富,此外,SPI设备的不同以及处理器对GPIO口位寻址是否支持各处理器各有不同,因而不同处理器中软件模拟GPIO也各不相同。若能提供一种通用可配置可移植的GPIO模拟SPI总线的驱动则能很方便快捷的访问SPI设备,从而提高整个嵌入式系统的开发效率。本文针对GPIO口位寻址与否给出方面,给出了一种可配置GPIO模拟SPI总线的方法并详细介绍了其设计与实现过程,且具有代码小可移植性强使用方便等特点。

1 GPIO规范

SPI是一个全双工的串行接口。它设计成可以在一个给定总线上处理多个互联的主机和从机。在一定数据传输过程中,接口上只能有一个丰机和一个从机能够通信。在一次数据传输中,主机总是向从机发送一个字节数据,而从机也总是向主要发送一个字节数据。可以使MCU与各种外围设备以串行方式进行通信以交换信息。由于SPI总线一共只需3~4位数据线和控制线即可实现与具有SPI总线接口功能的各种I/O器件进行接口,而扩展并行总线则需要8根数据线、8~16位地址线、2~3位控制线,冈此,采用SPI总线接口

可以简化电路设计,节省很多常规电路中的接口器件和I/O口线,提高设计的可靠性。在基于SPI总线接口构成的通信网络中,通信可由主节点发起,也可由从节点发起。当主节点发起通信时,它可主动对从节点进行数据的读写操作。工作过程叙述如下:首先选中要与之通信的从节点(通常片选端为低有效),而后送出时钟信号,读取数据信息的操作将在时钟的上升沿(或下降沿)进行。每送出八个时钟脉冲,从节点产生一个中断信号,该中断信号通知上节点一个字节已完整接收,可发送下一个字节的数据。SPI接口网络主从点需完成给出片选信号及时钟信号,它可主动的与各从节点进行信息的交流;而在从节点主动要求服务的情况下,它却是一种半主动的形式。由SPI接口技术构成的网络接口信号线(CLK、MOSI、MISO、/SS和INT)如果辅之以相应完备的通信协议,其服务功能必然会增强,相比于485等主从式分布网络而言,其通信速率也应有较人的提高。

2 GPIO模拟SPl

2.1 SPI硬件结构

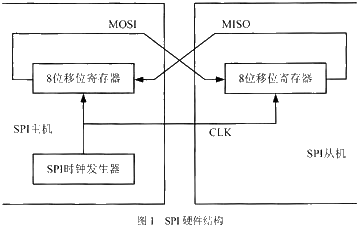

SPI接口在内部硬件实际上足两个简单的移位寄存器,传输的数据为8位,在主器件产生的从器件使能信号和移位脉冲下,按位传输,高位在前,低位在后,SPI内部硬件结构如图1所示。

2.2 SPI时序

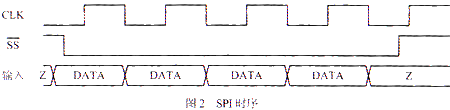

在SCLK的下降沿上数据改变,同时一位数据被存入移位寄存器,SPI时序如图2所示。

2.3 SPI写过程模拟

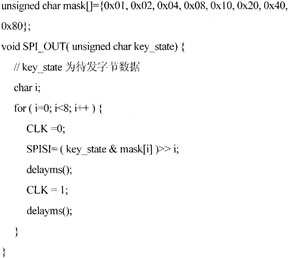

采用掩码方式实现位控制。

3 可配置GPIO设计与实现

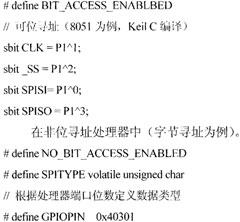

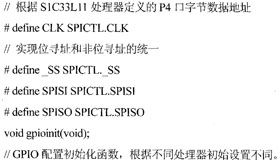

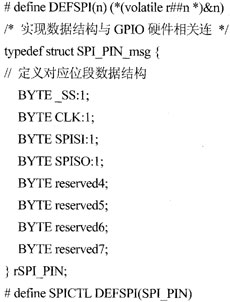

GPIO端口可分为支持位寻址和不支持位寻址,需由程序移植人员根据处理器及编译器情况定义GPIO对应的SPI接口,相关文件在SPIHARD.H中。

3.1 GPIO配置

3.2 实现配置的可移植部分

与GPIO口寻址方式无关性代码的实现。

以上实现在EPSON S1C33L11、AT89C52、SPCE061A及PHILIPS ARM LPC2106上都得到验证。