| 内容 |

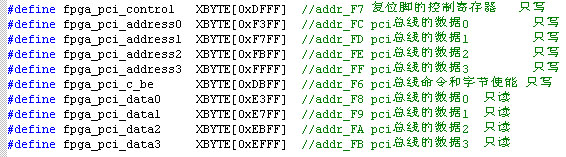

单片机控制PCI总线用了10个寄存器.EMP7128里建立了10个寄存器来控制PCI总线的操作.

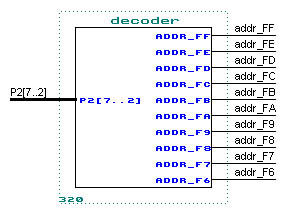

这10个寄存器的地址由6条地址线:P2.2,P2.3,P2.4,P2.5,P2.6,P2.7确定.输出addr_F6,addr_F7,

addr_F8,addr_F9,addr_FA,addr_FB,addr_FC,addr_FD,addr_FE,addr_FF共10个地址选通线.

输入输出示意图:

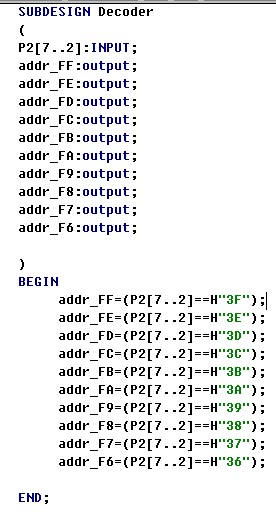

该译码的逻辑定义在我提供的文档的decoder.tdf文件里:

注解:如上图的逻辑定义,

当P2[7..2]=0x3f=111111 (二进制)时,addr_FF输出为高,其他为低.

当P2[7..2]=0x3e=111110 (二进制)时,addr_FE输出为高,其他为低.

当P2[7..2]=0x3d=111101 (二进制)时,addr_FD输出为高,其他为低.

当P2[7..2]=0x3c=111100 (二进制)时,addr_FC输出为高,其他为低.

当P2[7..2]=0x3b=111011 (二进制)时,addr_FB输出为高,其他为低.

当P2[7..2]=0x3a=111010 (二进制)时,addr_FA输出为高,其他为低.

当P2[7..2]=0x39=111001 (二进制)时,addr_F9输出为高,其他为低.

当P2[7..2]=0x38=111000 (二进制)时,addr_F8输出为高,其他为低.

当P2[7..2]=0x37=110111 (二进制)时,addr_F7输出为高,其他为低.

当P2[7..2]=0x36=110110 (二进制)时,addr_F6输出为高,其他为低.

这10条译码输出控制10个寄存器:

其中4个为只读,6个为只写.

实际上fpga_pci_address[3..0]和fpga_pci_data[3..0]是可以合并地址的,为了减少相互之间的干扰和控制线的稳定,才把读和写的地址分离的.

|