| 内容 |

关于PCI总线的标准PCI2.1(33Mhz) PCI2.2(66Mhz)的标准化文件可以在本站的下载特区下载.或者到官方的网站:http://www.pcisig.com下载.为英文的pdf文件,中文的PCI标准可以购买<<PCI系统结构(第四版)

>> 一书,电子工业出版社.中国电子网(http://www.21ic.com)也有一些关于PCI的文章,但是都比较简单,并没有很具体的对PCI进行论述.我们将陆续刊登一些文章,论述PCI总线,也可以给设计PCI板卡的做为参考.

RTL8029AS的芯片资料可以在这里下载.

RTL8029AS网卡(单口)电路图在这里下载.

RTL8029AS网卡(双口)电路图在这里下载.

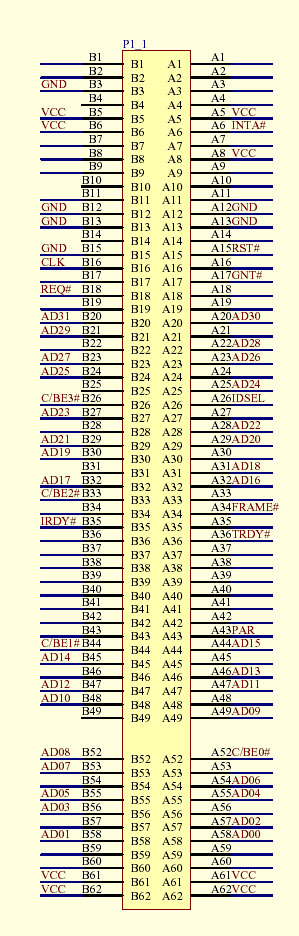

PCI卡的引脚定义图:

我们以PCI标准V2.1为蓝本来做说明,因为PCI V2.2是66Mhz的64 bit总线标准.RTL8029AS

PCI网卡只支持V2.1标准(33Mhz,32 bit) ,在上面的定义中,我省略了很多GND的引脚的定义,在标准的定义中,有很多的引脚被定义为GND,主要是用来做信号的屏蔽和隔离的作用.特别是对66Mhz的PCI总线.因为我们用到的总线的频率不高,连线也不长,可以不需要这些GND的引脚.去掉这些GND引脚的好处是方便布线.去掉这些引脚不会影响性能,因为在RTL8139(100Mhz)的网卡里,也是没有连接这些引脚的.

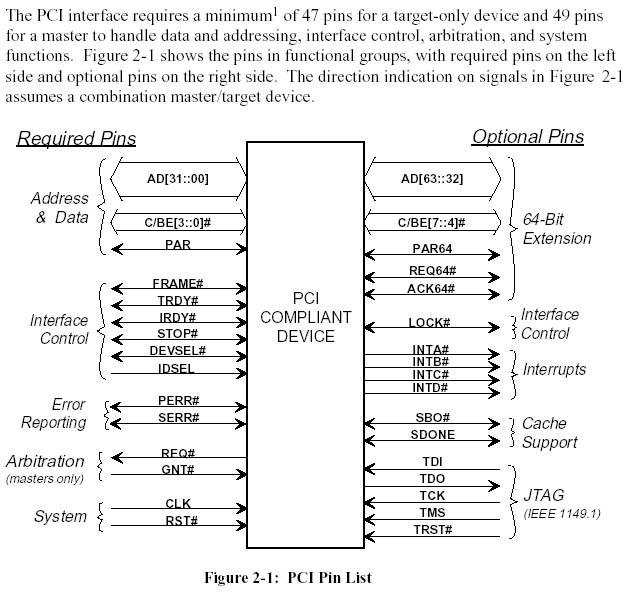

我们用的是PCI V2.1版 5伏的32位卡的标准.PCI卡分为主(Master),从(Target)两种类型,主卡可以控制PCI总线,从卡不能控制PCI总线.RTL8029AS网卡只能作为从卡,也就是说它只能作为Target,而不能做为主设备.标准的主设备至少有49条线跟PCI总线相连.从设备至少有47条线跟PCI总线相连.要支持中断的话,加一条INTA#引脚(共50或48条引脚).图中引脚名称中带#号的表示该引脚为低电平有效,不带#号的为高电平有效.INTA#是带"#"号的,表示低电平有效,就是说当它为低电平时引起中断,平时为高电平.

上图左边的为必须要的引脚,右边的为可选的引脚(我们可以都不用). 因为RTL8029AS只能作为target设备,所以上面的主设备才有的引脚(REQ#,GNT#),可以不用.(在我提供的demo里,这些引脚还是被连接到逻辑电路EPM7128S里(PAR等引脚也被连到CPLD里,为了将来可以使用RTL8139),但是事实上并没有用到,连到逻辑电路的目的是为了将来可能使用RTL8139(10M/100M自适应网卡)来代替10M的RTL8029AS网卡,因为RTL8139可以做为主设备进行DMA数据传输,所以需要这两个引脚,但是RTL8139需要的控制逻辑要比RTL8029AS复杂).

那么对于RTL8029AS来说,只要用从设备的48个引脚.是不是一定要这48条引脚呢?答案是还可以进行简化.下面我将做一个分析:

PAR引脚:PAR是奇偶校验引脚,校验AD[31..0]和C/BE[3..0]#.但是因为RTL8029AS不作奇偶校验,也不报告校验错误,因此该引脚也可以不要.

PERR#:为校验报告,因为RTL8029AS不作该报告,可以不要.

SERR#:系统错误报告,RTL8029AS同样不报告系统错误,可以不要.

DEVSEL#:为RTL8029AS的输出引脚,以表示地址译码有效.因为RTL8029AS最慢不会超过4个PCI时钟有效,

一般是第2个PCI时钟便有效.我们提供的demo的PCI的时钟为22.1184Mhz,而单片机的机器周期(总线速度)每秒只有22.1184/12=1.8432Mhz,比PCI总线慢12倍,也就是说不需要经过0.4个单片机的机器周期,RTL8029AS便会输出DEVSEL#有效.对单片机来说,网卡是随时准备好的.因此没有必要去判断该引脚,该引脚也可以不要.

TRDY#:为网卡输出的准备好的信号.网卡准备好最慢不会超过8个PCI时钟周期(不超过0.8个单片机机器周期), 对于单片机来说,网卡同样是随时准备好的.该引脚也可以不要.

STOP#:RTL8029AS没有这个引脚,所以可以不要.

那么PCI的接口信号就被简化为:

AD[31..0]

C/BE[3..0]#

FRAME#

IRDY#

IDSEL#

CLK

RST#

INTA#

共42条引脚,如果不想用中断方式来驱动网卡,那么中断INTA#也可以不要.我的demo 里还是将INTA#连到CPLD里.以方便用户使用.

去掉这些引脚的目的,是为了简化逻辑设计,altera提供的标准的PCI核一般至少需要440个LCELL,

相当于1万门以上的逻辑,必须使用FLEX10K,APEX20K等大容量的CPLD,而这些芯片都比较贵.而我使用的EMP7128才2500门(共128个LCELL),虽然我用的EPM7128有128个LCELL,但我只用了其中的67个

LCELL,用了不到1500门.可见简化接口有着非常重要的意义,就是简化逻辑,降低成本.

|